MACOM

#### **Applications**

- Serial Routing Switchers

- Distribution Amplifiers

- SMPTE Coaxial Cable Interface

- Studio video applications

- Broadcast video applications

- Distribution video applications

#### **Standards Compliance**

• SMPTE 259M, 292M, 344M and DVB-ASI

#### Features

- Data rate support for 143, 177, 270, 360, 540, 1483.5, 1485 Mbps and DVB-ASI at 270 Mbps

- · Auto and manual rate selection modes with rate indication in Auto

- 4:1 Input MUX and Loss of Lock (LOL) indicator

- Differential I/O with on chip termination resistors

- Selectable auto MUTE or BYPASS with manual BYPASS option

- Low typical power dissipation (400 mW @ 3.3V)

- 2.5V, or 3.3V power supply operation

- Extended temperature operation: -10°C to +85°C

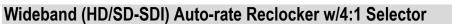

- 7 x 7 mm, 48-pin MLF package

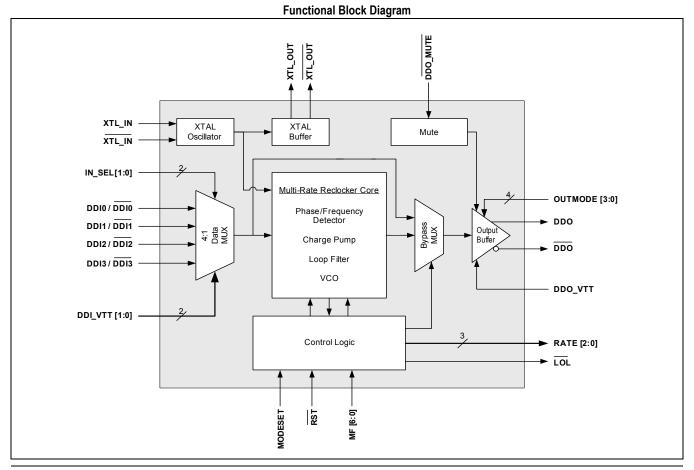

The M21235 is a high-speed, low-power reclocker designed to remove both random and inter-symbol interference (ISI) jitter from the retimed data for SMPTE (292M, 259M, 344M) and DVB-ASI serial digital video applications.

The M21235 design is based on a robust and proven reclocker architecture widely deployed in telecom and datacom systems. A custom and proprietary phase detector which combines the best of linear and non-linear phase detectors is used for high-jitter tolerance, especially, in the presence of duty-cycle-distortion (DCD) that typically arises with AC coupling and video pathological test patterns. The M21235 offers a variety of features that are accessible through multifunctional (MF) hardware pins or through a two-wire, I<sup>2</sup>C-compatible serial programming interface.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

## **Ordering Information**

| Part Number                              | Package                                   | Operating Temperature |

|------------------------------------------|-------------------------------------------|-----------------------|

| M21235G-34*                              | 48-pin, 7 mm x 7 mm MLF, (RoHS compliant) | –10 °C to 85 °C       |

| *The G in the part number indicates that | t this is an RoHS compliant package.      |                       |

## **Revision History**

| Revision | Level       | Date          | Description                                                                                                                                                 |

|----------|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

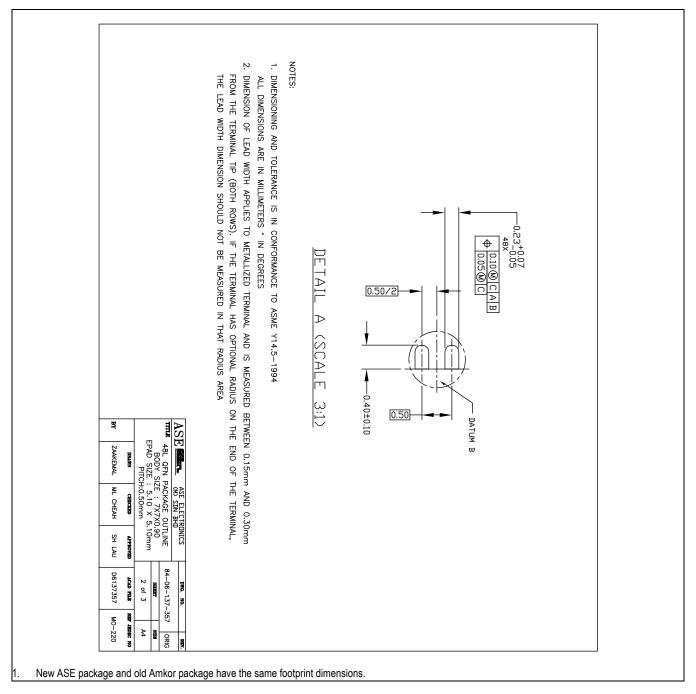

| V1       | Release     | December 2015 | Updated package drawing, Figure 1-1.<br>Package effective as of August 2014.<br>Added Figure 1-2.<br>Added marking diagram.<br>Removed preliminary markers. |

| V2P      | Preliminary | May 2015      | Updated logos and page layout. No content changes.                                                                                                          |

| C (V1P)  | Preliminary | May 2006      | Preliminary Release                                                                                                                                         |

| B (V2A)  | Advance     | May 2005      | General update33P added.                                                                                                                                    |

| A (V1A)  | Advance     | November 2004 | Initial Release                                                                                                                                             |

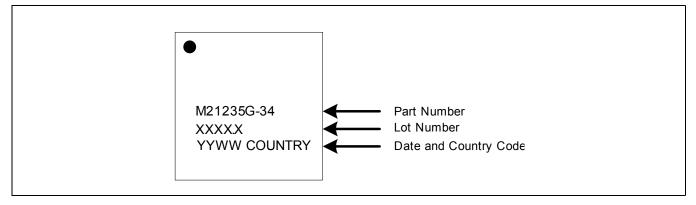

#### M21235 Marking Diagram

## **Table of Contents**

| Ordering Information            | n                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision History                |                                                                                                                                                                                                                                                                                                                                                                   |

| Table of Contents .             |                                                                                                                                                                                                                                                                                                                                                                   |

| 1.0 Product Spec                | ifications                                                                                                                                                                                                                                                                                                                                                        |

| 1.2Input/Ou1.3Reclocked         | Specifications       .5         tput Level Specifications:       .6         er Performance Specifications       .9         Specification       .11                                                                                                                                                                                                                |

| Ŭ                               | escription                                                                                                                                                                                                                                                                                                                                                        |

| 2.1 General  <br>2.1.1<br>2.1.2 | Description13Reclocker General Overview13Frequency Acquisition13riptions14General Nomenclature14Pin Descriptions142.2.2.1Power/Reset182.2.2.2Input Selection Multiplexer182.2.2.3High-Speed I/O Pins2.2.4Reclocker Reference Frequency192.2.2.5Reclocker Loop Bandwidth202.2.2.6Loss of Lock Alarm202.2.2.7Auto Rate Detect (ARD)202.2.2.8Bypass and DDO MUTE2121 |

| 2.2.3                           | Two-Wire Serial Interface                                                                                                                                                                                                                                                                                                                                         |

| 3.0 Registers                   |                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1 Register                    | Map.       24         Tables       25         Master Chip Reset       25         Chip Electronic ID.       25         Chip Revision Code       25         Reclocker Control - A.       26         Reclocker Control Register - B.       26                                                                                                                        |

<sup>3</sup>

#### Rev V1

|     | 3.2.6   | Reclocker Control Register - D. | . 27 |

|-----|---------|---------------------------------|------|

|     | 3.2.7   | Reclocker Control Register - E. | . 28 |

|     | 3.2.8   | Crystal Oscillator Control      | . 28 |

|     | 3.2.9   | Data Output Control - B         | . 29 |

|     | 3.2.10  | Loss of Signal (LOS) Control    | . 29 |

|     | 3.2.11  | Alarm Register (Read Only)      | . 30 |

|     | 3.2.12  | Status Register (Read Only)     | . 30 |

| A.1 | Glossar | y of Terms/Acronyms             | 31   |

| A.2 | Referen | ce Documents                    | 32   |

|     | A.2.1   | External                        | . 32 |

|     |         |                                 |      |

## **1.0 Product Specifications**

## 1.1 General Specifications

Table 1-1. Absolute Maximum Ratings

| Symbol              | Item                          | Item Minimum Maximu  |                       | Units |

|---------------------|-------------------------------|----------------------|-----------------------|-------|

| DV <sub>DD</sub>    | Digital I/O Power             | V <sub>SS</sub> -0.5 | V <sub>SS</sub> + 3.6 | V     |

| AV <sub>DD</sub>    | Analog I/O Power              | V <sub>SS</sub> -0.5 | V <sub>SS</sub> + 3.6 | V     |

| T <sub>STORE</sub>  | Storage Temperature           | -65                  | +150                  | ٥°    |

| ESD <sub>HBML</sub> | Human Body Model (low-speed)  | 2000                 | _                     | V     |

| ESD <sub>HBMH</sub> | Human Body Model (high-speed) | 2000                 | —                     | V     |

| ESD <sub>CDM</sub>  | Charge Device Model           | 500                  | —                     | V     |

| I <sub>DC</sub>     | Maximum DC Input Current      | —                    | 25                    | mA    |

| NOTE:               |                               |                      |                       |       |

| 1. No Damage        |                               |                      |                       |       |

#### Table 1-2. Recommended Operating Conditions

| Symbol           | Parameter                                                           | Notes | Minimum | Typical | Maximum | Units |  |  |

|------------------|---------------------------------------------------------------------|-------|---------|---------|---------|-------|--|--|

| AV <sub>DD</sub> | AV <sub>DD</sub> : Analog Power                                     | _     | 2.375   | 2.5/3.3 | 3.47    | V     |  |  |

| DV <sub>DD</sub> | DV <sub>DD</sub> : Digital Power                                    | _     | 2.375   | 2.5/3.3 | 3.47    | V     |  |  |

| V <sub>SS</sub>  | V <sub>SS</sub> : Chip Ground                                       | _     | _       | 0       | _       | V     |  |  |

| T <sub>AMB</sub> | Ambient Temperature                                                 | 1     | -10     | _       | +85     | °C    |  |  |

| $\theta_{JA}$    | Junction to ambient Thermal Resistance                              | 1     | _       | 29.4    | _       | °C/W  |  |  |

| NOTES:           | NOTES:                                                              |       |         |         |         |       |  |  |

| 1. Soldered of   | Soldered on multilayer board ( $\geq$ 4 layers), airflow = 0.0 m/s. |       |         |         |         |       |  |  |

Rev V1

#### Table 1-3. Power DC Electrical Specifications

| Symbol                  | Item                                                                                              | Notes   | Minimum | Typical | Maximum | Units |  |

|-------------------------|---------------------------------------------------------------------------------------------------|---------|---------|---------|---------|-------|--|

| Total I <sub>DD</sub>   | Total I <sub>DD</sub> (constant for all supply voltages)                                          | 1, 3    | -       | 122     | 140     | mA    |  |

| Total P <sub>DISS</sub> | Total P <sub>DISS</sub> (@2.5V)                                                                   | 1, 2, 3 | —       | 325     | 370     | mW    |  |

| Total P <sub>DISS</sub> | Total P <sub>DISS</sub> (@3.3V)                                                                   | 1, 2, 3 | —       | 430     | 485     | mW    |  |

| NOTES:                  |                                                                                                   |         | •       |         | •       |       |  |

| 1. Recommended          | . Recommended operating conditions - see Table 1-2.                                               |         |         |         |         |       |  |

| 2. Typical calculate    | . Typical calculated at nominal supply voltage, maximum calculated at nominal supply voltage +5%. |         |         |         |         |       |  |

| 3. Measured in ha       |                                                                                                   |         |         |         |         |       |  |

## 1.2 Input/Output Level Specifications:

#### Table 1-4. CMOS I/O Electrical Specifications

| Symbol          | Item                        | Notes | Minimum                | Typical          | Maximum                | Units |

|-----------------|-----------------------------|-------|------------------------|------------------|------------------------|-------|

| V <sub>OH</sub> | Output Logic High           | 1     | 0.8 x DV <sub>DD</sub> | DV <sub>DD</sub> | —                      | V     |

| V <sub>OL</sub> | Output Logic Low            | 1     | _                      | 0.0              | 0.2 x V <sub>DD</sub>  | V     |

| I <sub>OH</sub> | Output Current (logic high) | 1     | -10                    | _                | 0                      | mA    |

| I <sub>OL</sub> | Output Current (logic low)  | 1     | 0                      | _                | 10                     | mA    |

| V <sub>IH</sub> | Input Logic High            | 1     | 0.75 x V <sub>DD</sub> | _                | 3.6                    | V     |

| V <sub>IL</sub> | Input Logic Low             | 1     | 0                      | _                | 0.25 x V <sub>DD</sub> | V     |

| I <sub>IH</sub> | Input Current (logic high)  | 1     | -100                   | _                | 100                    | μΑ    |

| I               | Input Current (logic low)   | 1     | -100                   | _                | 100                    | μΑ    |

| t <sub>r</sub>  | Output Rise Time (20-80%)   | 1     | _                      | _                | 10                     | ns    |

| t <sub>f</sub>  | Output Fall Time (20-80%)   | 1     | _                      | _                | 10                     | ns    |

### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

Rev V1

| Symbol            | Parameter                                                                                    | Notes   | Minimum                | Typical | Maximum                | Units |

|-------------------|----------------------------------------------------------------------------------------------|---------|------------------------|---------|------------------------|-------|

| DR <sub>IN</sub>  | Input Bit Rate (reclocker bypassed)                                                          | 1       | 0                      | -       | 1500                   | Mbps  |

|                   | Input Bit Rate (reclocker enabled)                                                           | 1       | 143                    | —       | 1485                   | Mbps  |

| V <sub>ID</sub>   | Input Differential Voltage (peak - peak)                                                     | 1, 2, 3 | 100                    | —       | 2000                   | mV    |

| V <sub>ICM</sub>  | Input Common-Mode Voltage                                                                    | 1       | V <sub>SS</sub> + 1.15 | _       | AV <sub>DD</sub>       | V     |

| V <sub>IMAX</sub> | Maximum Input High Voltage                                                                   | 1       | —                      | —       | AV <sub>DD</sub> + 400 | mV    |

| V <sub>IMIN</sub> | Minimum Input Low Voltage                                                                    | 1       | V <sub>SS</sub> +1.0   | —       | —                      | V     |

| $\Delta V_{TT}$   | Max Common-Mode Voltage to DDI_VTT[1:0] Voltage difference                                   | 1       | —                      | —       | 600                    | mV    |

| R <sub>IN</sub>   | DDI_VTT[1:0] input termination impedance to AV <sub>DD</sub>                                 | 1       | 40                     | 50      | 60                     | Ω     |

| NOTES:            |                                                                                              |         |                        |         |                        |       |

| 1. Specit         | ied at recommended operation conditions - see Table 1-2                                      |         |                        |         |                        |       |

| 2. Exam           | ple 1200 mV <sub>pp</sub> differential = 600 mV <sub>pp</sub> for each single-ended terminal |         |                        |         |                        |       |

#### Table 1-5. High-Speed Input Electrical Specifications

3. Min. input level defined as error free operation at 10<sup>-12</sup> BER with PRBS input pattern

Rev V1

#### Table 1-6. Output Electrical Specifications

| CML Output Mode PC<br>Did<br>PC<br>Cc<br>Lo<br>Did | OUTMODE[3:2]<br>ommon Mode Voltage<br>OWERDOWN = 00b<br>ifferential Output Voltage<br>OWERDOWN = 00b<br>ommon Mode Voltage<br>ow Swing PCML = 01b | V <sub>OCM</sub> | Notes           1, 2           1, 2 | Minimum | floating                 | Maximum | Units            |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------|---------|--------------------------|---------|------------------|

| CML Output Mode PC<br>Dif<br>PC<br>Cc<br>Lo<br>Dif | OWERDOWN = 00b<br>ifferential Output Voltage<br>OWERDOWN = 00b<br>ommon Mode Voltage                                                              | V <sub>OD</sub>  |                                     |         | -                        |         |                  |

| PC<br>Cc<br>Lo<br>Dif                              | OWERDOWN = 00b                                                                                                                                    |                  | 1, 2                                |         | ٥                        |         |                  |

| Lo<br>Dif                                          | U                                                                                                                                                 | 14               | 1                                   |         | 0                        |         | V                |

|                                                    | 0                                                                                                                                                 | V <sub>OCM</sub> | 1, 2                                |         | AV <sub>DD</sub> - 0.175 |         | V                |

| Lo                                                 | ifferential Output Voltage<br>ow Swing PCML = 01b                                                                                                 | V <sub>OD</sub>  | 1, 2                                | 300     | 450                      | 600     | mV <sub>PP</sub> |

|                                                    | ommon Mode Voltage<br>edium Swing PCML = 10b                                                                                                      | V <sub>OCM</sub> | 1, 2                                |         | AV <sub>DD</sub> - 0.25  |         | V                |

|                                                    | ifferential Output Voltage<br>edium Swing PCML = 10b                                                                                              | V <sub>OD</sub>  | 1, 2                                | 600     | 800                      | 1000    | mV <sub>PP</sub> |

| Hig                                                | ommon Mode Voltage<br>igh Swing PCML = 11b<br>lefault Setting]                                                                                    | V <sub>OCM</sub> | 1, 2                                |         | AV <sub>DD</sub> - 0.5   |         | V                |

| Hig                                                | ifferential Output Voltage<br>igh Swing PCML = 11b<br>lefault Setting]                                                                            | V <sub>OD</sub>  | 1, 2, 3                             | 1300    | 1600                     | 2000    | mV <sub>PP</sub> |

| V <sub>DDO_TERM</sub> Te                           | ermination impedance to V <sub>DD</sub>                                                                                                           | R <sub>O</sub>   | 1                                   | 40      | 50                       | 60      | Ω                |

2. With  $50\Omega$  to AV<sub>DD</sub> termination.

3. Only valid with  $AV_{DD} = 3.3V$

#### Table 1-7. Reference Clock Input

| Symbol             | Parameter                                    | Notes | Minimum | Typical       | Maximum                | Units |

|--------------------|----------------------------------------------|-------|---------|---------------|------------------------|-------|

| F <sub>REF</sub>   | Input reference source or crystal rate       | 1, 2  | _       | 12.000/14.140 | _                      | MHz   |

| V <sub>REFIN</sub> | Input Differential Voltage Swing (peak-peak) | 1, 3  | 100     | 200           | 1600                   | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                    | 1, 3  | 250     | _             | AV <sub>DD</sub> -1200 | mV    |

| I <sub>DC</sub>    | Maximum DC input current                     | 1     | _       | _             | 15                     | mA    |

NOTES:

1. Specified at recommended operation conditions - see Table 1-2

- 2. The default value is 14.140 MHz crystal; however, a 12.00 MHz crystal can also be used (see text for more information)

- 3. Designed to accept a crystal, CMOS oscillator, or CMOS system clock. CMOS oscillator or system clock can be single-ended or differential

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

## 1.3 Reclocker Performance Specifications

| Symbol            | Parameter                                                                     | Notes            | Minimum | Typical | Maximum | Units |

|-------------------|-------------------------------------------------------------------------------|------------------|---------|---------|---------|-------|

| J <sub>ERMS</sub> | Reclocker Enabled Output Data Jitter @ 1.485 Gbps (RMS)                       | 1, 2, 3          | _       | 5.5     | 9       | ps    |

| $J_{EP-P}$        | Reclocker Enabled Output Data Jitter @ 1.485 Mbps (pp)                        | 1, 2, 3          | _       | 56      | 80      | mUI   |

| J <sub>EP-P</sub> | Reclocker Enabled Output Data Jitter @ < 600 Mbps (pp)                        | 1, 2, 3          | _       | —       | 40      | mUI   |

| J <sub>BRMS</sub> | Reclocker Bypassed Output Data Jitter @ 1.485 Gbps (RMS)                      | 1, 2, 3          | -       | 5       | _       | ps    |

| J <sub>BP-P</sub> | Reclocker Bypassed Output Data Jitter @ 1.485 Gbps (pp)                       | 1, 2, 3          | _       | _       | 52      | mUI   |

| J <sub>BP-P</sub> | Reclocker Bypassed Output Data Jitter @ < 600 Mbps (pp)                       | 1, 2, 3          | -       | _       | 30      | mUI   |

| NOTES:            | 1                                                                             |                  |         |         | I       |       |

| 1. Specifi        | ed at recommended operation conditions - see Table 1-2                        |                  |         |         |         |       |

| 2. All jitte      | r is measured using a 2 <sup>23</sup> -1 PRBS pattern, and/or HD/SD-SDI color | bar test pattern | l.      |         |         |       |

| 2 11              | r in managurad using a widehand approx (minimum 10 CHz handwidth              |                  |         |         |         |       |

#### Table 1-8. Reclocker Output Jitter Performance

All jitter is measured using a wideband scope (minimum 10 GHz bandwidth).

Rev V1

| Symbol            | Parameter                                          | Notes | Minimum | Typical | Maximum | Units |

|-------------------|----------------------------------------------------|-------|---------|---------|---------|-------|

| DR <sub>IN</sub>  | Input Bit Rate (NRZ data - Reclocker enabled)      | 1, 2  | 143     | _       | 1485    | Mbps  |

| J <sub>TOL</sub>  | Input jitter tolerance (10 Hz to 0.5 x LBW)        | 1, 3  | 1.2     | -       | -       | UI    |

| J <sub>TOL</sub>  | Input jitter tolerance (1.5xLBW to 10 MHz)         | 1, 3  | 0.6     | -       | -       | UI    |

| J <sub>GRMS</sub> | Jitter Generation (rms) @ 1.485 Gbps               | 1, 3  | -       | 6       | _       | mUI   |

| J <sub>GP-P</sub> | Jitter Generation (pp) @ 1.485 Gbps                | 1, 3  | _       | 36      | -       | mUI   |

| LBW <sub>HD</sub> | Loop bandwidth LBW_INC[1:0] = 11b at 1.485 Gbps    | 1     | _       | _       | 1.5     | MHz   |

| LBW <sub>HD</sub> | Loop bandwidth LBW_INC[1:0] = 10b at 1.485 Gbps    | 1     | _       | _       | 3.5     | MHz   |

| LBW <sub>HD</sub> | Loop bandwidth LBW_INC[1:0] = 00b at 1.485 Mbps    | 1     | _       | _       | 5       | MHz   |

| $LBW_SD$          | Loop bandwidth LBW_INC[1:0] = 11b at 270 Mbps      | 1     | _       | _       | 0.520   | MHz   |

| LBW <sub>SD</sub> | Loop bandwidth LBW_INC[1:0] = 10b at 270 Mbps      | 1     | _       | _       | 1       | MHz   |

| $LBW_SD$          | Loop bandwidth LBW_INC[1:0] = 00b at 270 Mbps      | 1     | -       | -       | 1.4     | MHz   |

| LBW <sub>PK</sub> | Loop bandwidth peaking (270 - 1485 Mbps)           | 1     | -       | 0.1     | -       | dB    |

| t <sub>LKA</sub>  | Asynchronous Lock (Auto Rate Detect lock time)     | 1, 4  | -       | 2       | 3       | ms    |

| t <sub>LKS</sub>  | Synchronous Switch Lock TIme @ 1.485 Gbps          | 1, 4  | -       | 110     | 150     | ns    |

| t <sub>LKS</sub>  | Synchronous Switch Lock TIme @ 270 Mbps            | 1, 4  | -       | 330     | 400     | ns    |

| IOTES:            | •                                                  | 1     |         |         | 1       |       |

|                   | at recommended operating condition – see Table 1-2 |       |         |         |         |       |

#### Table 1-9. Reclocker High-speed Performance

2. Represents guaranteed VCO tuning range

3. Jitter tolerance, Jitter Generation with PRBS 2<sup>23</sup>-1 or SMPTE color bar test pattern

4. Assume that reference is within +/-250ppm of desired data rate

Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

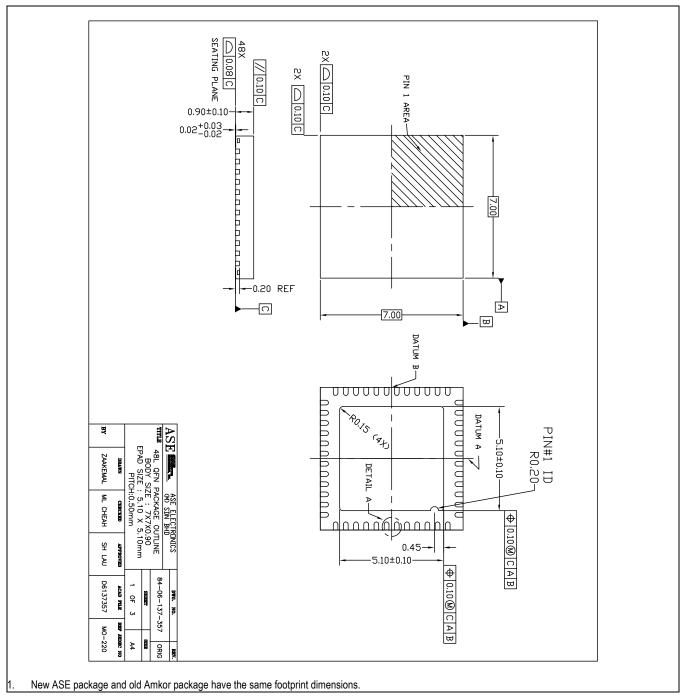

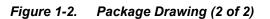

## 1.4 Package Specification

#### Figure 1-1. Package Drawing (1 of 2)

<sup>11</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V1

#### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

Rev V1

## 2.0 Functional Description

## 2.1 General Description

## 2.1.1 Reclocker General Overview

The reclocker is a dual loop based design. The primary phase locked loop (PLL) functions to 1) lock the VCO to the incoming data rate and 2) to retime the incoming data to remove jitter and is typically referred to as the clock and data recovery block (CDR). In general, the VCO tuning range for a multi-rate design is typically much larger than the frequency pull-in range of the CDR phase detector. As a result, a secondary frequency locked loop (FLL) is added to tune the VCO to the approximate data frequency so the CDR can lock onto valid data. The FLL uses an external crystal as an absolute frequency reference. As a result, the external reference is only used to assist the CDR frequency locking and the jitter performance of the reference has no effect on the recovered data output jitter.

## 2.1.2 Frequency Acquisition

In general, when the reclocker is out of lock ( $\overline{LOL}$  = Low), the FLL is enabled. The FLL then drives the VCO towards a frequency that is close to the incoming data rate frequency.

In principle, the FLL is shut off when the VCO approaches the data frequency. When FLL is shut off, **LOL** = High, to indicate a lock condition. If valid data is present, then the CDR will lock to the incoming data. When in lock, the FLL control circuit continues to monitor the frequency difference between VCO and the reference and if the difference is too large, a loss of lock condition is indicated and frequency acquisition is initiated.

Rev V1

## 2.2 Pin Descriptions

#### 2.2.1 General Nomenclature

Through out this data sheet, physical pins will be denoted in **bold** print. An array of pins can be called by each individual pin name (e.g. **MF0**, **MF1**, **MF2**, **MF3**, and **MF6**) or as an array (e.g. **MF[3:0, 6]**).

## 2.2.2 Pin Descriptions

#### Table 2-1. Control/Interface/Low-Speed Pins (1 of 3)

| Pin Name        | Pin #      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Default            | Туре            |

|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|

| XTL_IN/XTL_IN   | 39, 40     | Reference clock or crystal input. Upon power-up, this block defaults to the 14.140 MHz series resonance crystal. This can be changed to the 12.000 MHz parallel resonance crystal configuration through the appropriate software control register.                                                                                                                                                                                                                                                                                                                                                                                            | -                  | Analog<br>Input |

| XTL_OUT/XTL_OUT | 38, 37     | Reference frequency output for chained reclocker applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                  | 0               |

| IN_SEL[1:0]     | 14, 13     | Input control signal that selects the active high-speed serial input.<br>00: Select DDI0/DDI0<br>01: Select DDI1/DDI1<br>10: Select DDI2/DDI2<br>11: Select DDI3/DDI3                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Internal pull down | I-CMOS          |

| MF4/ARD_EN      | 46         | Input control signal that enables Auto Rate Detect (ARD) functionality or manual rate setting mode.<br><b>ARD_EN</b> = High: Auto Rate Detector (ARD) enabled<br><b>ARD_EN</b> = Low: Manual rate selection mode<br>When the M21235 is in SW mode, this pin is used for Address 2 of the I <sup>2</sup> C programming interface.                                                                                                                                                                                                                                                                                                              | Internal pull up   | I-CMOS          |

| RATE[2:0]       | 18, 17, 16 | Bidirectional control signals used to indicate the data rate in ARD enabled mode or to force a data rate setting in Manual mode.       Internal pull         ARD_EN = High: RATE[2:0] pins indicate the date rate the M21235 is locked to according to pin decoding shown below:       ARD_EN = Low: RATE[2:0] pins are used to force a particular data rate according to the pin decoding shown below:         000: 143 Mbps data rate       001: 177 Mbps data rate         010: 270 Mbps data rate       011: 360 Mbps data rate         100: 540 Mbps data rate       111: Reclocker not locked and data is bypassed from input to output |                    | I/O-CMOS        |

14

Rev V1

| Pin Name        | Pin #  | Function                                                                                                                                                       | Default          | Туре    |

|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|

| LOL             | 20     | Output Status indication signal for reclocker Loss of Lock. See the Section 2.1.2,<br>"Frequency Acquisition," on page 13 for more detailed information.       | -                | O-CMOS  |

|                 |        | LOL = High: Reclocker PLL is locked                                                                                                                            |                  |         |

|                 |        | <b>LOL</b> = Low: Reclocker PLL is not locked                                                                                                                  |                  |         |

| SD/HD           | 25     | Output status indication signal to control slew rate of downstream cable driver.<br>When the reclocker is unlocked, this pin defaults to LOW.                  | -                | O-CMOS  |

|                 |        | <b>SD</b> / <del>HD</del> = High: Reclocker locked to a SD data rate (143-540 Mbps)                                                                            |                  |         |

|                 |        | SD/HD = Low: Reclocker locked to a HD rate (1.4835/1.485 Gbps)                                                                                                 |                  |         |

| MF5/AUTO_BYPASS | 47     | Input control signal that automatically bypasses the data directly from the input to the output if the Reclocker PLL can NOT lock to the incoming data stream. | Internal pull up | I-CMOS  |

|                 |        | AUTO_BYPASS = High: Auto bypass reclocker if lock is not achieved                                                                                              |                  |         |

|                 |        | AUTO_BYPASS = Low: Reclocker continues to attempt data lock but output data BER may be high                                                                    |                  |         |

|                 |        | Address 3 of I <sup>2</sup> C interface when device is in SW mode.                                                                                             |                  |         |

| MF1/MAN_BYPASS  | 43     | Input control signal used to force a reclocker PLL bypass regardless of the setting of the AUTO_BYPASS signal.                                                 | Internal pull up | I- CMOS |

|                 |        | MAN_BYPASS = High: Force bypass (regardless of AUTO_BYPASS state)                                                                                              |                  |         |

|                 |        | MAN_BYPASS = Low: Enables normal AUTO_BYPASS operation                                                                                                         |                  |         |

|                 |        | SDA for the I <sup>2</sup> C interface when device is in SW mode.                                                                                              |                  |         |

| MF2/LBW_INC[0]  | 26     | Input control signal used to increase the Loop Bandwidth from the nominal setting.                                                                             | Internal pull up | I-CMOS  |

|                 |        | LBW_INC[0] = High or Floating: Normal operation                                                                                                                |                  |         |

|                 |        | LBW_INC[0] = Low: Increased bandwidth                                                                                                                          |                  |         |

|                 |        | Address 0 of I <sup>2</sup> C interface when device is in SW mode.                                                                                             |                  |         |

| MF3/LBW_INC[1]  | 45     | Input control signal that can be used to increase LBW. Refer to Table 2-4.                                                                                     | Internal pull up | I-CMOS  |

|                 |        | LBW_INC[1] = High: Normal LBW (floating default)                                                                                                               |                  |         |

|                 |        | LBW_INC[1] = Low: Increased bandwidth                                                                                                                          |                  |         |

|                 |        | Address 1 of I <sup>2</sup> C interface when device is in SW mode.                                                                                             |                  |         |

| OUTMODE[1:0]    | 23, 30 | In HW mode, selects the type of output mode (reserved for future use).                                                                                         | Internal pull up | I-CMOS  |

|                 |        | 00: CML output                                                                                                                                                 |                  |         |

|                 |        | 01: Reserved<br>10: Reserved                                                                                                                                   |                  |         |

|                 |        |                                                                                                                                                                |                  |         |

|                 |        | 11: Reserved                                                                                                                                                   |                  |         |

<sup>15</sup>

## Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

Rev V1

| Pin Name     | Pin #  | Function                                                               | Default          | Туре   |

|--------------|--------|------------------------------------------------------------------------|------------------|--------|

| OUTMODE[3:2] | 22, 29 | In HW mode, selects the swing for the high-speed output buffers.       | Internal pull up | I-CMOS |

|              |        | 00: Power down                                                         |                  |        |

|              |        | 01: 500 mV                                                             |                  |        |

|              |        | 10: 800 mVpp                                                           |                  |        |

|              |        | 11: 1600 mV                                                            |                  |        |

| MF6          | 48     | Address 4 of the I <sup>2</sup> C interface when device is in SW mode. | Internal pull up | I-CMOS |

| MF0          | 42     | 42 SCL for the I <sup>2</sup> C interface when device is in SW mode.   |                  | I-CMOS |

| RST          | 24     | Hardware reset pin. Need to pull down to issue reset.                  | Internal pull up | I-CMO  |

| MODESET      | 28     | HW/SW Mode Select pin:                                                 | Internal pull up | I-CMO  |

|              |        | MODESET = High: HW control mode                                        |                  |        |

|              |        | MODESET = Low: SW control mode                                         |                  |        |

| DTE:         | 1      |                                                                        | I                | I      |

#### Table 2-2. Power Pins

| Pin Name         | Pin #                        | Function                                                                    | Туре            |

|------------------|------------------------------|-----------------------------------------------------------------------------|-----------------|

| V <sub>SS</sub>  | PAD                          | Chip Ground. Paddle must be soldered to PCB using an array of thermal vias. | Power           |

| AV <sub>DD</sub> | 6, 15, 19, 21, 27, 35,<br>41 | Power Supply.                                                               | Power (Analog)  |

| DV <sub>DD</sub> | 44                           | Power Supply.                                                               | Power (Digital) |

#### Table 2-3. High-speed Signal Pins

| Pin Name     | Pin #                      | Function                                                                                                                                                                                                | Default                  | Туре         |

|--------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|

| DDI/DDI[3:0] | 1, 3, 4, 5, 7, 8, 9,<br>11 | Internally terminated. Non-inverting and inverting high speed serial data inputs.                                                                                                                       | $100\Omega$ differential | I-High-speed |

| DDI_VTT[1:0] | 2,10                       | Input termination pin (center tap for 50 $\Omega$ ).<br>Case 1: Tie to a positive supply for 50 $\Omega$ to supply terminal<br>Case 2: Leave floating and decouple to gnd for 100 $\Omega$ differential |                          | Term         |

| DDO/DDO      | 33, 31                     | Internally terminated. Non-inverting and inverting high speed serial data outputs.                                                                                                                      | $100\Omega$ differential | O-High-speed |

| DDO_VTT      | 32                         | Output termination center tap. Tie to a positive supply for $50\Omega$ to supply termination.                                                                                                           |                          | Term         |

<sup>16</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

The M21235 is available in a 48-pin 7 mm x 7 mm MLF package. The pin out is shown in Figure 2-1 and the package drawing in Figure 1-1 and Figure 1-2. Regular (with Pb) or RoHS compliant options available.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

## MACOM

Rev V1

#### 2.2.2.1 Power/Reset

The M21235 is designed to work at an extended power supply range from 1.8 to 3.3V for further reduction of power and to simplify the interface to the next generation of ASICs. The M21235 reclocker automatically resets after power up thus an external reset is not required. The M21235 is fully operational 10 ms after the power supply has stabilized to within 10% of the final value. An external hardware reset pin **RST** is provided for manually resetting the device or it may be reset through the control register using the  $I^2C$  interface.

#### 2.2.2.2 Input Selection Multiplexer

The M21235 contains a 4:1 input selection multiplexer. The **IN\_SEL[1:0]** pins select one of the four possible inputs that will be retimed by the reclocker block and passed to the output. The mapping of the multiplexer <u>pin is shown in</u> Table 2-1. If the **IN\_SEL[1:0]** pins are left floating, the 4:1 input multiplexer defaults to input **DDI[0]/DDI[0]**.

#### 2.2.2.3 High-Speed I/O Pins

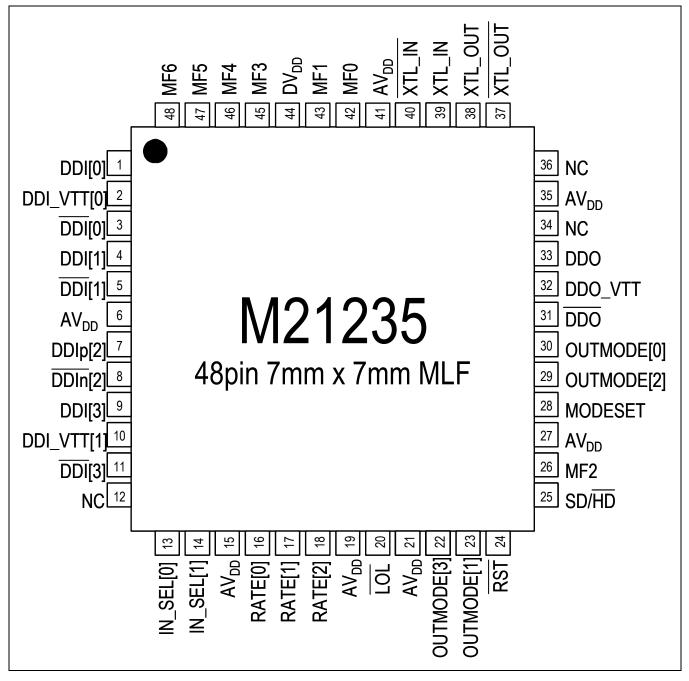

The high-speed inputs are designed to be used in both AC coupled and DC coupled modes. The high-speed differential inputs contain on-chip  $50\Omega$  termination from **DDI[n]** to **DDI\_TERM[n]** as well as from **DDI[n]** to **DDI\_VTT[n]**. Figure 2-2 shows the recommended connection of the **DDI\_VTT[n]** pin for AC coupled inputs or with DC coupled CML when the CML is driven from the same supply voltage. For use in other DC coupled situations, it is recommended that the termination voltage for the M21235 be set at the input common mode level and that the common mode and input swing falls within the specified range as shown in Table 1-5. **DDI\_TERM[n]** contains a weak internal bias near **AV<sub>DD</sub>**, and should be decoupled to **V<sub>SS</sub>** to reduce input noise with a 10 nF capacitor.

Figure 2-2. Input circuit for M21235

The high-speed output contains integrated  $50\Omega$  resistors from both **DDO** and **DDO** to **VDDO\_TERM**. **VDDO\_TERM** should be bypassed to **V**<sub>SS</sub> with a 10nF capacitor. **VDDO\_TERM** is internally biased to **AV**<sub>DD</sub>.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V1

#### 2.2.2.4 Reclocker Reference Frequency

The reclocker frequency acquisition requires an external frequency source applied to **XTL\_IN/XTL\_IN**. The M21235 reference input can be a standard crystal, a crystal oscillator with CMOS/TTL single ended outputs, or a differential PCML/LVDS/LVPECL system clock. For daisy-chained reclocker applications, a buffered reference output is made available on **XTL\_OUT/XTL\_OUT**.

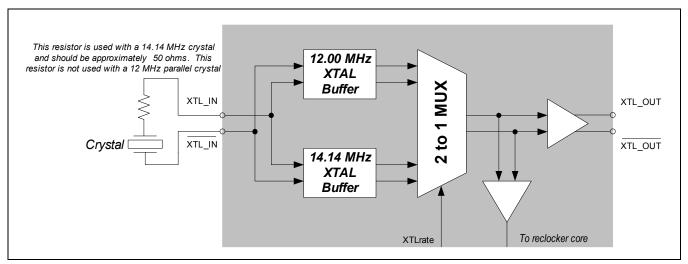

The input reference frequency can be either 12.000 MHz or 14.140 MHz. By default, the M21235 expects a 14.140 MHz series resonance crystal. The M21235 can also be used with a 12.000 MHz parallel resonance reference crystal which was selected based on the SD/HD-SDI bitrates as well as the fact that the 12.000 MHz is a common-stocked low cost standard rate crystal. A 56 $\Omega$  resistor is recommended for the series resonance case and the series resistor is set to 0 ohms for the 12.00 MHz parallel resonance crystal. Bits[5:4] of register address 08h are used to configure the M21235 to operate with a parallel or series crystal.

When a 14.14 MHz series or 12.00 MHz parallel resonant crystal is used with the M21215, the crystal should be connected as shown in Figure 2-3 below.

#### Figure 2-3. Application circuit when a series or parallel resonant crystal is used

The series resonant crystal should operate at 14.14 MHz with a frequency stability of +/- 50 ppm or better, equivalent series resistance of  $80\Omega$  or less, drive level of < 0.2 mW, and static capacitance of less than 5.0 pF. The parallel resonant crystal should operate at 12.00 MHz with a frequency stability of +/- 50 ppm or better, equivalent series resistance of  $80\Omega$  or less, drive level of < 0.2 mW, and static capacitance of less than 5.0 pF.

The M21235 can also operate with a reference from an external clock buffer or oscillator instead of a crystal. The M21235 can accept a single ended or differential 14.14 MHz reference clock, and a single ended 12.00 MHz reference clock. When driving the M21235 with a single ended reference clock, the clock signal should be connected to the **XTL\_IN** pin and the **XTL\_IN** pin should be left floating. If a 14.14 MHz reference clock is used, the **XTAL\_MODE [1:0]** bits should be set to '11', and if a 12.00 MHz reference clock is used, the **XTAL\_MODE [1:0]** bits should be set to '10'. If the **XTL\_IN** pins on the M21235 are connected to a clock driver or oscillator, the requirements for the signal connected to the M21235 are detailed in Table 1-7.

By default 14.140MHz operation is used.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V1

#### 2.2.2.5 Reclocker Loop Bandwidth

For SD-SDI rates, the loop bandwidth scales proportionately to the bit rate, using the 270 Mbps as a reference point. For example, at 540 Mbps, the bandwidth is 2x the 270 Mbps bandwidth. When **LBW\_INC[0]** = Low, the bandwidth increases to 3.5 MHz for 1485 Mbps data rates and 1 MHz for 270 Mbps data rates.

For improved synchronous lock time, the M21235 offers a still higher loop bandwidth option of 5 MHz for 1485 Mbps data rates and 1.4 MHz for 270 Mbps data rates when **LBW\_INC[0]** and **LBW\_INC[1]** =Low.

| LBW_INC[1]                                         | LBW_INC[0] | LOOP BANDWIDTH (1,485 Mbps) | LOOP BANDWIDTH (270 Mbps) |  |

|----------------------------------------------------|------------|-----------------------------|---------------------------|--|

| 0                                                  | 0          | 5.0 MHz                     | 1.4 MHz                   |  |

| 0                                                  | 1          | 5.0 MHz                     | 1.4 MHz                   |  |

| 1                                                  | 0          | 3.5 MHz                     | 1.0 MHz                   |  |

| 1                                                  | 1          | 1.5 MHz (default)           | 520 KHz (default)         |  |

| NOTE:                                              |            |                             |                           |  |

| Scales to lower frequency with reduced data rates. |            |                             |                           |  |

Table 2-4.

Loop Bandwidth Control Setting (in H/W control mode)

#### 2.2.2.6 Loss of Lock Alarm

A los<u>s of lock alarm pin</u>,  $\overline{LOL}$ , is provided to indicate if the reclocker is in lock. When the reclocker has achieved lock, LOL = High. If the reclocker is out of lock, LOL = Low. For synchronous switching at the same data rate, the lock time is lower if a higher loop bandwidth is selected.

#### 2.2.2.7 Auto Rate Detect (ARD)

The M21235 is designed to operate in two modes. In the first mode, with **ARD\_EN** = High, the Auto Rate Detect is enabled which automatically locks the CDR to the rates typically used in SD-SDI, HD-SDI, and DVB-ASI applications. The locked to data rate is then reported with **RATE[2:0]** pins as shown in Table 2-5.

With the ARD disabled (**ARD\_EN** = Low), the reclocker locking frequency is forced by using the **RATE[2:0]** pins as inputs and selecting the data rate as shown in Table 2-6. In this case, there are two additional non-standard rates that are supported by the M21235 part.

| RATE[2:0] | Bit Rate         |

|-----------|------------------|

| 000       | 143 Mbps         |

| 001       | 177 Mbps         |

| 010       | 270 Mbps         |

| 011       | 360 Mbps         |

| 100       | 540 Mbps         |

| 101       | 1485/1483.5 Mbps |

| 111       | Unlocked         |

Table 2-5.

Rate Report Mapping when ARD is Enabled

20

| RATE[2:0] | Bit Rate              |  |

|-----------|-----------------------|--|

| 000       | 143 Mbps              |  |

| 001       | 177 Mbps              |  |

| 010       | 270 Mbps              |  |

| 011       | 360 Mbps              |  |

| 100       | 540 Mbps              |  |

| 101       | 1485/1483.5 Mbps      |  |

| 110       | Non-standard 140 Mbps |  |

| 111       | Non-standard 155 Mbps |  |

#### Table 2-6. Rate Select with ARD Disabled

For system reporting purposes as well as to set the output slew rate on the <u>cable</u> drivers, the **SD/HD** output is used to indicate if the reclocker has locked to a HD rate. For SD-SDI rates, **SD/HD** = High and for the HD-SDI rate **SD/HD** = Low.

To improve on the asynchronous lock times, the M21235 offers several options with the ARD algorithm.

**177Iockout** = High would remove the 177 Mbps rate from the search sequence resulting in a slightly faster asynchronous lock time but as there are not any false locking issues with DVB-ASI with the M21235 this is not required.

Also, if the M21235 is out-of-lock, the search pattern will not start unless the M21235 detects that there are transitions in the data through an internal loss of signal detector. To reduce the lock time even further, the M21235 offers several alternative ARD search sequences that are set with the **ARD\_FN[1:0]** register control bits and these are summarized in Table 2-7.

| ARD_FN[1:0]  | M21235 Additional ARD Search Sequences              |  |

|--------------|-----------------------------------------------------|--|

| 11 (default) | start->143->177->270->360->540->1483.5/1485->repeat |  |

| 10           | start->270->360->540->1485/1483.5->repeat           |  |

| 01           | start->270->360->1485/1483.5->repeat                |  |

| 00           | start->270->1485/1483.5->repeat                     |  |

### 2.2.2.8 Bypass and DDO\_MUTE

The reclocker can be forced into the bypass mode (input data to output without retiming) with **MAN\_BYPASS** = High. With **MAN\_BYPASS** = Low (normal operation), **AUTO\_BYPASS** = High enables the auto bypass mode that puts the reclocker into the bypass mode whenever **LOL** = Low (i.e. the reclocker is out of lock).

This implies that if both **MAN\_BYPASS** and **AUTO\_BYPASS** = Low, when the reclocker is not in lock, unlocked data will appear at the output. This mode may be used for troubleshooting or debug purposes.

Rev V1

<sup>21</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

#### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

Rev V1

When the reclocker is not in a bypass state, the output can be forced to a logic low with **DDO\_MUTE** = Low. This function can be used to squelch the noise output.

| MAN_BYPASS | AUTO_BYPASS | Functional Description          |

|------------|-------------|---------------------------------|

| 0          | 0           | Retimed Reclocker Output        |

| 0          | 1           | Bypass if Reclocker out of lock |

| 1          | 0           | Forced Bypass                   |

| 1          | 1           | Forced Bypass                   |

Table 2-8.Manual and Auto Bypass Setting

To prevent the propagation of noise in the case where there is an LOL condition, the RCLK contains an auto-inhibit feature, which is enabled by setting bit 3 (autoinh\_en) in Reclocker Control A register to a logic 1. When LOL is active, the output at DDO is fixed at a logic low state. By default this feature is disabled.

## 2.2.3 Two-Wire Serial Interface

The two-wire serial interface is compatible with the  $I^2C$  standard. The M21235 supports the read/write slave-only mode, 5-bit device address field width, and supports the standard rate of 100 Kbps, fast mode of 400 Kbps, and high-speed mode of 3.4 Mbps. The 5-bit address for the device is determined with **MF [6:2]**, which allows for a maximum of 32 unique addresses for this device. SDA (**MF1**) and SCL (**MF0**) can drive a maximum of 500 pF each at the maximum rate. During the write mode from the master to the M21235, data is latched into the internal M21235 registers on the rising edge of SCL, during the acknowledge phase (ACK) of communication. Table 2-9 summarizes the multifunction pins for the two-wire serial interface mode. For further information on timing, please see the  $I^2C$  bus specification standard.

| Pin | Function      | Description                                |

|-----|---------------|--------------------------------------------|

| MF0 | SCL           | Clock input (open drain)                   |

| MF1 | SDA           | Data input/output (open drain)             |

| MF2 | Address bit 0 | 5-bit device address; address bit 0 is LSB |

| MF3 | Address bit 1 | 5-bit device address; address bit 1        |

| MF4 | Address bit 2 | 5-bit device address; address bit 2        |

| MF5 | Address bit 3 | 5-bit device address; address bit 3        |

| MF6 | Address bit 4 | 5-bit device address; address bit 4 is MSB |

Table 2-9.

Multifunction Pins for Two-Wire Interface in SW Control Mode

| Pin | Function      | Description                                                |

|-----|---------------|------------------------------------------------------------|

| MF0 | N/C           | Not used in HW mode.                                       |

| MF1 | Manual Bypass | Used to force reclocker into bypass mode.                  |

| MF2 | LBW_INC[0]    | Used to increase the loop bandwidth. Refer to Table 2-4.   |

| MF3 | LBW_INC[1]    | Used to increase the loop bandwidth. Refer to Table 2-4.   |

| MF4 | ARDEN         | Used to enable Auto Rate Detect functionality.             |

| MF5 | Auto Bypass   | Used to force reclocker into bypass mode when out of lock. |

| MF6 | Vss           | Connect to Vss in HW mode.                                 |

#### Table 2-10. Multifunction Pins in HW Control Mode

## 3.0 Registers

## 3.1 Register Map

#### Table 3-1. Register Summary

| Addr | Register<br>Name | d7: MSB     | d6          | d5           | d4                | d3          | d2          | d1          | d0: LSB     | Register<br>Default |

|------|------------------|-------------|-------------|--------------|-------------------|-------------|-------------|-------------|-------------|---------------------|

|      | Common Registers |             |             |              |                   |             |             |             |             |                     |

| 00h  | mastreset        | rst         | rst         | rst          | rst               | rst         | rst         | rst         | rst         | 00h                 |

| 01h  | chipcode         | chipcode[7] | chipcode[6] | chipcode[5]  | chipcode[4]       | chipcode[3] | chipcode[2] | chipcode[1] | chipcode[0] | 77h                 |

| 02h  | revcode          | revcode[7]  | revcode[6]  | revcode[5]   | revcode[4]        | revcode[3]  | revcode[2]  | revcode[1]  | revcode[0]  | 22h                 |

|      |                  |             |             |              | Reclocker Registe | rs          |             |             |             |                     |

| 03h  | RCLK_ctrlA       | softreset   | Clear_alarm | RSVD         | RSVD              | autoinh_en  | RSVD        | RSVD        | RSVD        | 87h                 |

| 04h  | RCLK_ctrlB       | RSVD        | RSVD        | RSVD         | BW[1]             | BW[0]       | RSVD        | RSVD        | MAN_bypass  | 44h                 |

| 06h  | RCLK_ctrID       | RSVD        | RSVD        | ARDen        | ARD_FN[1]         | ARD_FN[0]   | RATE_SEL[2] | RATE_SEL[1] | RATE_SEL[0] | 3Dh                 |

| 07h  | RCLK_ctrlE       | RSVD        | RSVD        | RSVD         | DDO_MUTE          | 177lockout  | autobypass  | Insel[1]    | Insel[0]    | 74h                 |

| 08h  | Xtal_ctrl        | RSVD        | RSVD        | Xtal_mode[1] | Xtal_mode[0]      | RSVD        | RSVD        | RSVD        | RSVD        | 35h                 |

| 0Ah  | Dout_ctrlB       | RSVD        | RSVD        | RSVD         | RSVD              | Out_lvl[1]  | Out_lvI[0]  | Out_mode[1] | Out_mode[0] | 3Ch                 |

| 0Eh  | los_ctrl         | RSVD        | RSVD        | RSVD         | LOS_DISABLE       | RSVD        | Los_lvl[2]  | Los_lvl[1]  | Los_lvl[0]  | 40h                 |

| 13h  | alarm_reg (LH)   | SDxHD       | RSVD        | lol          | RSVD              | RSVD        | RSVD        | RSVD        | los         | N/A                 |

| 14h  | RATE             | RSVD        | RATE[2]     | RATE[1]      | RATE[0]           | RSVD        | RSVD        | RSVD        | RSVD        | N/A                 |

Register Table Details:

1. Do not write to undefined register addrsses – operation not guaranteed.

2. RSVD Internal: Defines register bits for MACOM use only: Must always write the default value MPSD internal bits. When in doubt, read back default value after reset.

## 3.2 Register Tables

### 3.2.1 Master Chip Reset

#### Table 3-2. Master Chip Reset (mastreset: Address 00h)

| Bits | Туре | Default | Label | Description                                                           |

|------|------|---------|-------|-----------------------------------------------------------------------|

| 7:0  | W    | 0h      | rst   | Same feature has hardware <b>RST</b> . Resets entire IC. (Write only) |

|      |      |         |       | AAh: Reset upon write to this register with AAh.                      |

|      |      |         |       | 00h: Normal operation                                                 |

|      |      |         |       | All other values are ignored.                                         |

### 3.2.2 Chip Electronic ID

#### Table 3-3. Chip Electronic ID (chipcode: Address 01h)

| Bits | Туре | Default | Label    | Description                                             |

|------|------|---------|----------|---------------------------------------------------------|

| 7:0  | R    | 77h     | chipcode | This read only register contains the ID of this device. |

## 3.2.3 Chip Revision Code

#### Table 3-4. Chip Revision Code (RevCode: Address 02h)

| Bits | Туре | Default | Label   | Description                                                |

|------|------|---------|---------|------------------------------------------------------------|

| 7:0  | R    | 24h     | revcode | This read only register contains the revision of the part. |

|      |      |         |         | Format is A.B where A is the main rev and B is the sub rev |

|      |      |         |         | Default value is 22h for Rev 1.0                           |

## Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

## 3.2.4 Reclocker Control - A

| Bits | Туре | Default | Label       | Description                                                                                                                                    |

|------|------|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | R/W  | 1       | softreset   | Resets the reclocker only (Setup registers remain unchanged, need to softreset after rate change)<br>0: Reset RCLK only<br>1: Normal Operation |

| 6    | R/W  | 0       | clear_alarm | Clear alarm registers<br>0: Normal Operation<br>1: Clear all alarm registers, see Table 3-12                                                   |

| 5    | R/W  | 0       | RSVD        | For MACOM use only. Must be set to 0                                                                                                           |

| 4    | R/W  | 0       | RSVD        | For MACOM use only. Must be set to 0                                                                                                           |

| 3    | R/W  | 0       | autoinh_en  | Autoinhibit enable<br>0: Autoinhibit disabled<br>1: Inhibit data output to low when reclocker issues an out of lock or loss of signal alarm    |

| 2    | R/W  | 1       | RSVD        | For MACOM use only. Must be set to 1                                                                                                           |

| 1    | R/W  | 1       | RSVD        | For MACOM use only. Must be set to 1                                                                                                           |

| 0    | R/W  | 1       | RSVD        | For MACOM use only. Must be set to 1                                                                                                           |

#### Table 3-5. Reclocker Control - A (RCLK\_ctrlA: Address 03h)

## 3.2.5 Reclocker Control Register - B

#### Table 3-6. Reclocker Control Register - B (RCLK\_ctrlB: Address 04h)

| Bits | Туре | Default | Label        | Description                                                                                                                                                                                                                                                     |

|------|------|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | R/W  | 010     | RSVD         | For MACOM use only. Must be set to 010b.                                                                                                                                                                                                                        |

| 4:3  | R/W  | 00      | LBW_INC[1:0] | Nominal Loop BW control           00: HD: BW = 1.5 MHz, SD @ 270 MHz BW = 0.52 MHz           01: HD: BW = 3.5 MHz, SD @ 270 MHz BW = 0.52 MHz           10: HD BW = 5.0 MHz, SD @ 270 MHz BW = 1.0 MHz           11: HD BW = 5.0 MHz, SD @ 270 MHz BW = 1.4 MHz |

| 2    | R/W  | 1       | RSVD         | For MACOM use only. Must be set to 1                                                                                                                                                                                                                            |

| 1    | R/W  | 0       | RSVD         | For MACOM use only. Must be set to 0                                                                                                                                                                                                                            |

| 0    | R/W  | 0       | MAN_BYPASS   | Forces the reclocker to bypass the input to the output without retiming<br>0: Normal operation (Retimed data out)<br>1: Force Bypass                                                                                                                            |

26

### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

## 3.2.6 Reclocker Control Register - D

| Bits | Туре | Default | Label         | Description                                         |

|------|------|---------|---------------|-----------------------------------------------------|

| 7:6  | R/W  | 00      | RSVD          | For MACOM use only. Must be set to 00b.             |

| 5    | R/W  | 1       | ARD_EN        | Auto rate detection enable/disable                  |

|      |      |         |               | 0: Auto rate detect OFF                             |

|      |      |         |               | 1: Auto rate detect ON                              |

| 4:3  | R/W  | 11      | ARD_FN[1:0]   | Sets the ARD search order and bit rate (repeated)   |

|      |      |         |               | 00: 270 -> 1485Mb/s                                 |

|      |      |         |               | 01: 270 -> 360 -> 1485 Mb/s                         |

|      |      |         |               | 10: 270 -> 360 -> 540 -> 1485 Mb/s                  |

|      |      |         |               | 11: 143 -> 177 -> 270 -> 360 -> 540 -> 1485 Mb/s    |

| 2:0  | R/W  | 101     | RATE_SEL[2:0] | Data rate information for manual HW mode (ARD_EN=0) |

|      |      |         |               | 000: 143 Mb/s                                       |

|      |      |         |               | 001: 177 Mb/s                                       |

|      |      |         |               | 010: 270 Mb/s                                       |

|      |      |         |               | 011: 360Mb/s                                        |

|      |      |         |               | 100: 540Mb/s                                        |

|      |      |         |               | 101: 1483.5/1485b/s                                 |

|      |      |         |               | 110: 140 Mb/s                                       |

|      |      |         |               | 111: 155 Mb/s                                       |

|      |      |         |               | Note: Used to manually force a given data rate.     |

Table 3-7.

Reclocker Control Register - D (RCLK\_ctrlD: Address 06h)

### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

## 3.2.7 Reclocker Control Register - E

| Bits | Туре | Default | Label       | Description                                                |

|------|------|---------|-------------|------------------------------------------------------------|

| 7:5  | R/W  | 011     | RSVD        | For MACOM use only. Must be set to 011b                    |

| 4    | R/W  | 1       | DDO_MUTE    | Inhibit data outputs                                       |

|      |      |         |             | 0: Inhibit to low                                          |

|      |      |         |             | 1: Normal mode                                             |

| 3    | R/W  | 0       | 177lockout  | Disable 177Mb/s rate from auto detection circuit           |

|      |      |         |             | 0: Do not disable 177Mb/s rate from auto detection circuit |

|      |      |         |             | 1: Disable 177Mb/s rate from auto detection circuit        |

| 2    | R/W  | 1       | AUTO_BYPASS | Bypass reclocker when out of lock                          |

|      |      |         |             | 0: Do not bypass when out of lock                          |

|      |      |         |             | 1: Bypass reclocker when out of lock                       |

| 1:0  | R/W  | 00      | IN_SEL[1:0] | Input channel select                                       |

|      |      |         |             | IN_SEL[1:0]Input Channel Selected                          |

|      |      |         |             | 00SDI [0]                                                  |

|      |      |         |             | 01SDI [1]                                                  |

|      |      |         |             | 10SDI [2]                                                  |

|      |      |         |             | 11SDI [3]                                                  |

#### Table 3-8. Reclocker Control Register - E (cdr\_ctrlE00: Address 07h)

## 3.2.8 Crystal Oscillator Control

#### Table 3-9. Crystal Oscillator Control (Xtal\_ctrl: Address 08h)

| Bits | Туре | Default | Label          | Description                                       |

|------|------|---------|----------------|---------------------------------------------------|

| 7:6  | R/W  | 00      | RSVD           | For MACOM use only. Must be set to 00b            |

| 5:4  | R/W  | 11      | xtal_mode[1:0] | Reclocker reference clock modes                   |

|      |      |         |                | 00: Power down XTAL oscillators                   |

|      |      |         |                | 01: Parallel mode XTAL oscillator (12.00MHz) ON   |

|      |      |         |                | 10: Bypass XTAL oscillators, apply external clock |

|      |      |         |                | 11: Serial mode XTAL oscillator ON (14.14MHz)     |

| 3:0  | R/W  | 0101    | RSVD           | For MACOM use only. Must be set to 0101.          |

### Wideband (HD/SD-SDI) Auto-rate Reclocker w/4:1 Selector

### 3.2.9 Data Output Control - B

| Bits | Туре | Default | Label         | Description                                                                                                                         |

|------|------|---------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7:4  | R/W  | 0011    | RSVD          | For MACOM use only. Must be set to 0010b                                                                                            |

| 3:2  | R/W  | 11      | out_lvl[1:0]  | Setting     Swing       00:     Power down     0 mV       01:     Low swing     500 mV       10:     Medium swing     800 mV (LVDS) |

|      |      |         |               | 11: High swing 1600 mV                                                                                                              |

| 1:0  | R/W  | 00      | out_mode[1:0] | Output buffer mode<br>00: CML<br>01: Reserved<br>10: Reserved<br>11: Reserved                                                       |

#### Table 3-10. Data Output Control - B (DoutCtrlB: Address 0Ah)

See Table 1-6 for details.

## 3.2.10 Loss of Signal (LOS) Control

#### Table 3-11. Loss of Signal (LOS) Control (Los\_ctrl: Address 0Eh)

| Bits | Туре | Default | Label        | Description                                                                                                                         |

|------|------|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | R/W  | 010     | RSVD         | For MACOM use only. Must be set to 010                                                                                              |

| 4    | R/W  | 0       | LOS_DISABLE  | Enable/Disable LOS detection circuit<br>0: LOS detection enabled<br>1: LOS detection disabled                                       |