# PWM Controller and Transformer Driver with Quad-Channel Isolators

**Data Sheet**

### ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

#### **FEATURES**

Isolated PWM controller Integrated transformer driver

Regulated adjustable output: 3.3 V to 24 V

2 W output power

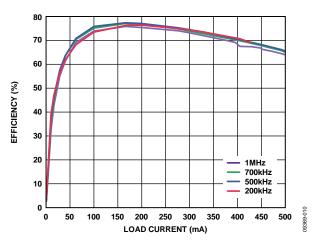

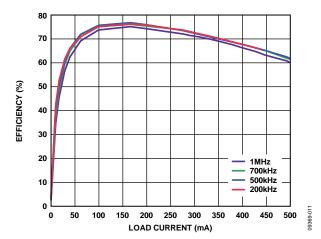

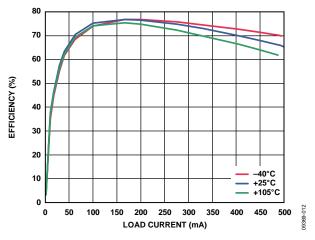

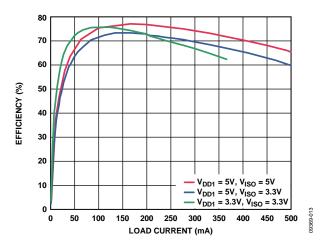

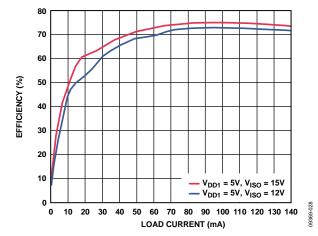

70% efficiency at guaranteed load of 400 mA at 5.0 V output

Quad dc-to-25 Mbps (NRZ) signal isolation channels

20-lead SSOP package

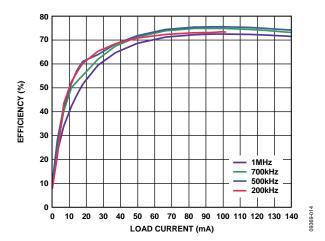

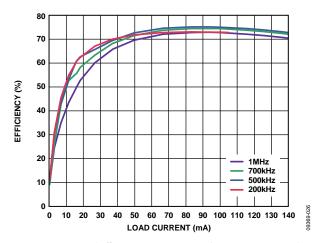

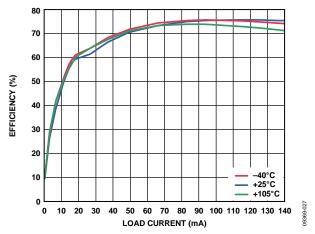

High temperature operation: 105°C maximum High common-mode transient immunity: >25 kV/μs 200 kHz to 1 MHz adjustable oscillator frequency

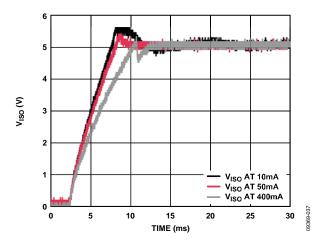

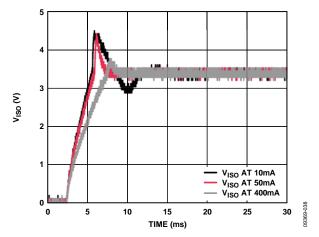

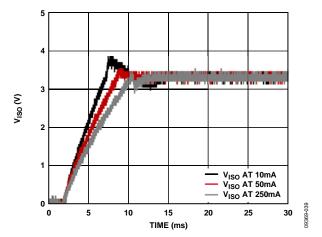

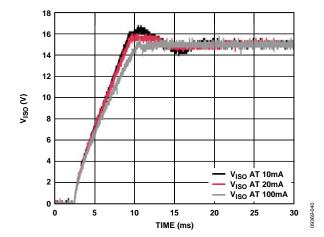

Soft start function at power-up

Pulse-by-pulse overcurrent protection

Thermal shutdown

#### Safety and regulatory approvals

UL recognition: 2500 V rms for 1 minute per UL 1577

**CSA Component Acceptance Notice #5A**

**VDE** certificate of conformity

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

$V_{IORM} = 560 V peak$

**Qualified for automotive applications**

#### **APPLICATIONS**

RS-232/RS-422/RS-485 transceivers Industrial field bus isolation Power supply start-up bias and gate drives Isolated sensor interfaces Process controls Automotive

#### **GENERAL DESCRIPTION**

#### The ADuM3470/ADuM3471/ADuM3472/ADuM3473/

ADuM3474 devices¹ are quad-channel digital isolators with an integrated PWM controller and transformer driver for an isolated dc-to-dc converter. Based on the Analog Devices, Inc., *i*Coupler® technology, the dc-to-dc converter provides up to 2 W of regulated, isolated power at 3.3 V to 24 V from a 5.0 V input supply or from a 3.3 V supply. This eliminates the need for a separate, isolated dc-to-dc converter in 2 W isolated designs. The *i*Coupler chip scale transformer technology is used to isolate the logic signals, and the integrated transformer driver with isolated secondary side control provides higher efficiency for the isolated dc-to-dc converter. The result is a small form factor, total isolation solution. The ADuM347x isolators provide four independent isolation channels in a variety of channel configurations and data rates (see the Ordering Guide).

#### <sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329. Other patents pending.

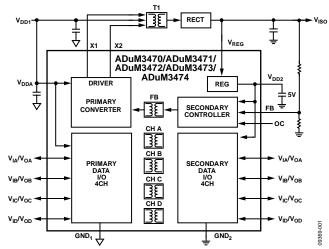

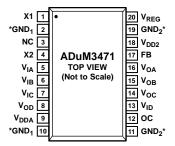

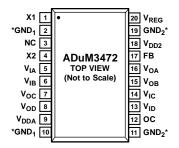

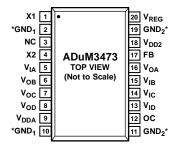

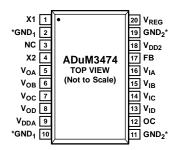

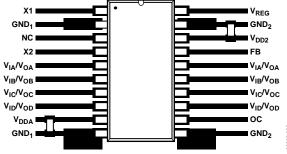

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1. Functional Block Diagram

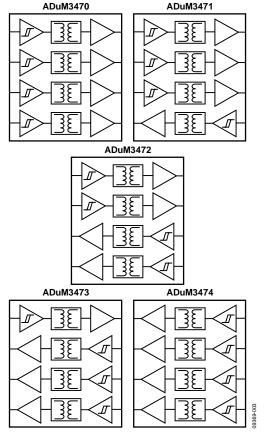

Figure 2. Block Diagrams of I/O Channels

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

### **TABLE OF CONTENTS**

| Features 1                                                                             | Typical Performance Characteristics                      | 19 |

|----------------------------------------------------------------------------------------|----------------------------------------------------------|----|

| Applications1                                                                          | Terminology                                              | 24 |

| General Description1                                                                   | Applications Information                                 | 25 |

| Functional Block Diagrams1                                                             | Application Schematics                                   | 25 |

| Revision History                                                                       | Transformer Design                                       | 26 |

| Specifications                                                                         | Transformer Turns Ratio                                  |    |

| Electrical Characteristics—5 V Primary Input Supply/                                   | Transformer ET Constant                                  |    |

| 5 V Secondary Isolated Supply                                                          | Transformer Primary Inductance and Resistance            | 27 |

| Electrical Characteristics—3.3 V Primary Input Supply/ 3.3 V Secondary Isolated Supply | Transformer Isolation Voltage                            |    |

|                                                                                        | Switching Frequency                                      | 27 |

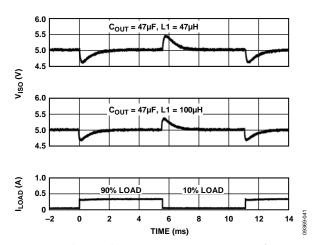

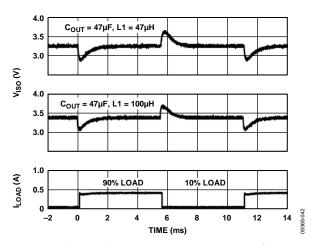

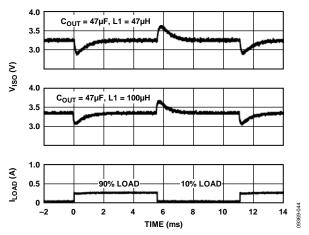

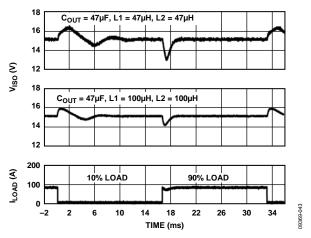

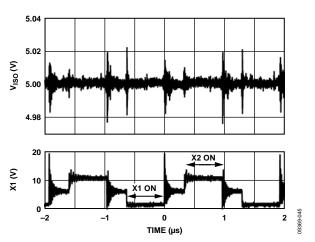

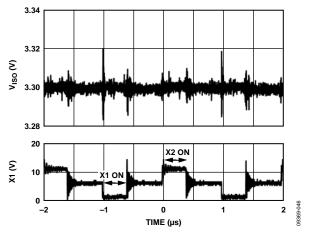

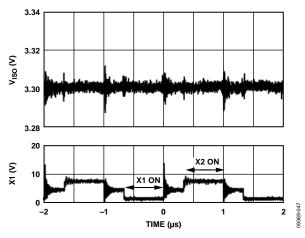

| Electrical Characteristics—5 V Primary Input Supply/ 3.3 V Secondary Isolated Supply7  | Transient Response                                       | 27 |

| Electrical Characteristics—5 V Primary Input Supply/                                   | Component Selection                                      | 27 |

| 15 V Secondary Isolated Supply9                                                        | Printed Circuit Board (PCB) Layout                       | 28 |

| Package Characteristics11                                                              | Thermal Analysis                                         | 28 |

| Regulatory Approvals11                                                                 | Propagation Delay-Related Parameters                     |    |

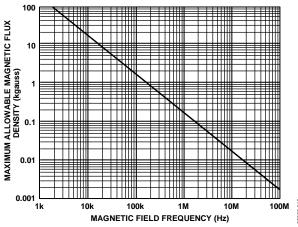

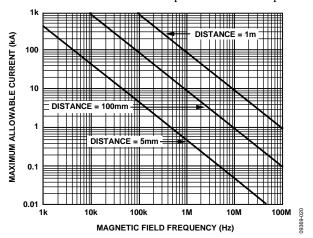

| Insulation and Safety-Related Specifications11                                         | DC Correctness and Magnetic Field Immunity               |    |

| DIN V VDE V 0884-10 (VDE V 0884-10):2006-12                                            | Power Consumption                                        |    |

| Insulation Characteristics                                                             | Power Considerations                                     |    |

| Recommended Operating Conditions 12                                                    | Insulation Lifetime                                      |    |

| Absolute Maximum Ratings13                                                             | Outline Dimensions                                       |    |

| ESD Caution                                                                            |                                                          |    |

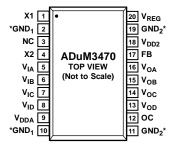

| Pin Configurations and Function Descriptions14                                         | Ordering Guide                                           |    |

|                                                                                        | Automotive i roducto                                     | 55 |

| REVISION HISTORY                                                                       |                                                          |    |

| 5/14—Rev. A to Rev. B                                                                  | Changes to Figure 6 and Table 14                         | 16 |

| Change to Table 49                                                                     | Changes to Figure 7 and Table 15                         |    |

|                                                                                        | Changes to Figure 8, Table 16, and Table 17              |    |

| 7/13—Rev. 0 to Rev. A                                                                  | Change to Figure 9                                       |    |

| Changed V <sub>DD1</sub> Pin to NC PinThroughout                                       | Changes to Terminology Section                           |    |

| Changes to Features Section, Applications Section,                                     | Changes to Applications Information Section, Application |    |

| General Description Section, and Figure 11                                             | Schematics Section, Figure 38, Figure 39, and Figure 40  |    |

| Created Hyperlink for Safety and Regulatory Approvals                                  | Changes to Transformer Turns Ratio Section               | 26 |

| Entry in Features Section                                                              | Changes to Transformer ET Constant Section,              |    |

| Changes to Table 1                                                                     | Transient Response Section, and Table 19                 |    |

| Changes to Table 25                                                                    | Changes to Figure 41                                     |    |

| Changes to Table 37                                                                    | Changes to Power Consumption Section and Figure 45       |    |

| Changes to Table 49                                                                    | Changes to Insulation Lifetime Section and Figure 48     |    |

| Changes to Regulatory Approvals Section11                                              | Changes to Ordering Guide                                |    |

| Changes to Figure 3 and Table 9                                                        | Added Automotive Products Section                        | 33 |

| Changes to Figure 4 and Table 1214                                                     |                                                          |    |

| Changes to Figure 5 and Table 1315                                                     | 10/10—Revision 0: Initial Version                        |    |

### **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS—5 V PRIMARY INPUT SUPPLY/5 V SECONDARY ISOLATED SUPPLY**

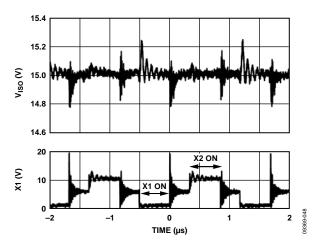

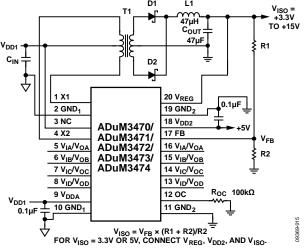

$4.5~V \le V_{DD1} = V_{DDA} \le 5.5~V; V_{DD2} = V_{REG} = V_{ISO} = 5.0~V; f_{SW} = 500~kHz;$  all voltages are relative to their respective grounds (see the application schematic in Figure 38). All minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at  $T_A = 25^{\circ}C$ ,  $V_{DD1} = V_{DDA} = 5.0~V$ ,  $V_{DD2} = V_{REG} = V_{ISO} = 5.0~V$ .

Table 1.

| Parameter                                                             | Symbol                  | Min   | Тур  | Max   | Unit   | Test Conditions/Comments                                                                        |

|-----------------------------------------------------------------------|-------------------------|-------|------|-------|--------|-------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTER POWER SUPPLY                                       |                         |       |      |       |        |                                                                                                 |

| Isolated Output Voltage                                               | V <sub>ISO</sub>        | 4.5   | 5.0  | 5.5   | V      | $I_{ISO} = 0 \text{ mA}, V_{ISO} = V_{FB} \times (R1 + R2)/R2$                                  |

| Feedback Voltage Setpoint                                             | $V_{FB}$                | 1.125 | 1.25 | 1.375 | V      | $I_{ISO} = 0 \text{ mA}$                                                                        |

| Line Regulation                                                       | V <sub>ISO (LINE)</sub> |       | 1    | 10    | mV/V   | $I_{ISO} = 50 \text{ mA}, V_{DD1} = 4.5 \text{ V to } 5.5 \text{ V}$                            |

| Load Regulation                                                       | V <sub>ISO (LOAD)</sub> |       | 1    | 2     | %      | I <sub>ISO</sub> = 50 mA to 200 mA                                                              |

| Output Ripple                                                         | V <sub>ISO (RIP)</sub>  |       | 50   |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                 |

| Output Noise                                                          | V <sub>ISO (N)</sub>    |       | 100  |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                 |

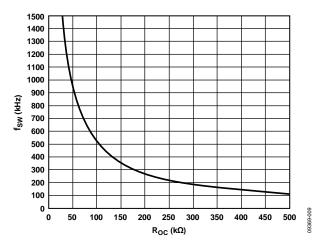

| Switching Frequency                                                   | f <sub>sw</sub>         |       | 1000 |       | kHz    | $R_{OC} = 50 \text{ k}\Omega$                                                                   |

|                                                                       |                         |       | 200  |       | kHz    | $R_{OC} = 270 \text{ k}\Omega$                                                                  |

|                                                                       |                         | 192   | 318  | 515   | kHz    | $V_{OC} = V_{DD2}$ (open loop)                                                                  |

| Switch On Resistance                                                  | Ron                     |       | 0.5  |       | Ω      |                                                                                                 |

| Undervoltage Lockout, V <sub>DD1</sub> , V <sub>DD2</sub><br>Supplies |                         |       |      |       |        |                                                                                                 |

| Positive Going Threshold                                              | $V_{UV+}$               |       | 2.8  |       | V      |                                                                                                 |

| Negative Going Threshold                                              | $V_{UV-}$               |       | 2.6  |       | V      |                                                                                                 |

| Hysteresis                                                            | V <sub>UVH</sub>        |       | 0.2  |       | V      |                                                                                                 |

| DC to 2 Mbps Data Rate <sup>1</sup>                                   |                         |       |      |       |        | f ≤ 1 MHz                                                                                       |

| Maximum Output Supply Current <sup>2</sup>                            | I <sub>ISO (MAX)</sub>  | 400   |      |       | mA     | $V_{ISO} = 5.0 \text{ V}$                                                                       |

| Efficiency at Maximum Output<br>Supply Current <sup>3</sup>           |                         |       | 70   |       | %      | I <sub>ISO</sub> = I <sub>ISO</sub> (MAX)                                                       |

| <i>i</i> COUPLER DATA CHANNELS                                        |                         |       |      |       |        |                                                                                                 |

| DC to 2 Mbps Data Rate <sup>1</sup>                                   |                         |       |      |       |        |                                                                                                 |

| IDD1 Supply Current, No VISO Load                                     | I <sub>DD1 (Q)</sub>    |       |      |       |        | $I_{ISO} = 0 \text{ mA, } f \le 1 \text{ MHz}$                                                  |

| ADuM3470                                                              |                         |       | 14   | 30    | mA     |                                                                                                 |

| ADuM3471                                                              |                         |       | 15   | 30    | mA     |                                                                                                 |

| ADuM3472                                                              |                         |       | 16   | 30    | mA     |                                                                                                 |

| ADuM3473                                                              |                         |       | 17   | 30    | mA     |                                                                                                 |

| ADuM3474                                                              |                         |       | 18   | 30    | mA     |                                                                                                 |

| 25 Mbps Data Rate (C Grade Only)                                      |                         |       |      |       |        |                                                                                                 |

| IDD1 Supply Current, No VISO Load                                     | I <sub>DD1 (D)</sub>    |       |      |       |        | $I_{ISO} = 0 \text{ mA}, C_L = 15 \text{ pF}, f = 12.5 \text{ MHz}$                             |

| ADuM3470                                                              |                         |       | 44   |       | mA     |                                                                                                 |

| ADuM3471                                                              |                         |       | 46   |       | mA     |                                                                                                 |

| ADuM3472                                                              |                         |       | 48   |       | mA     |                                                                                                 |

| ADuM3473                                                              |                         |       | 50   |       | mA     |                                                                                                 |

| ADuM3474                                                              |                         |       | 52   |       | mA     |                                                                                                 |

| Available V <sub>ISO</sub> Supply Current <sup>4</sup>                | I <sub>ISO (LOAD)</sub> |       |      |       |        | $C_L = 15 \text{ pF, } f = 12.5 \text{ MHz}$                                                    |

| ADuM3470                                                              |                         |       | 390  |       | mA     | •                                                                                               |

| ADuM3471                                                              |                         |       | 388  |       | mA     |                                                                                                 |

| ADuM3472                                                              |                         |       | 386  |       | mA     |                                                                                                 |

| ADuM3473                                                              |                         |       | 384  |       | mA     |                                                                                                 |

| ADuM3474                                                              |                         |       | 382  |       | mA     |                                                                                                 |

| I <sub>DD1</sub> Supply Current, Full V <sub>ISO</sub> Load           | I <sub>DD1 (MAX)</sub>  |       | 550  |       | mA     | $C_L = 0 \text{ pF, } f = 0 \text{ MHz, } V_{DD1} = 5 \text{ V,}$<br>$I_{ISO} = 400 \text{ mA}$ |

| Parameter                                                    | Symbol                                                                       | Min                                 | Тур   | Max  | Unit  | Test Conditions/Comments                                 |

|--------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-------|------|-------|----------------------------------------------------------|

| I/O Input Currents                                           | I <sub>IA</sub> , I <sub>IB</sub> , I <sub>IC</sub> , I <sub>ID</sub>        | -20                                 | +0.01 | +20  | μΑ    |                                                          |

| Logic High Input Threshold                                   | V <sub>IH</sub>                                                              | 2.0                                 |       |      | V     |                                                          |

| Logic Low Input Threshold                                    | V <sub>IL</sub>                                                              |                                     |       | 0.8  | V     |                                                          |

| Logic High Output Voltages                                   | V <sub>OAH</sub> , V <sub>OBH</sub> ,<br>V <sub>OCH</sub> , V <sub>ODH</sub> | $V_{DD1} - 0.3,$<br>$V_{ISO} - 0.3$ | 5.0   |      | V     | $I_{Ox} = -20 \ \mu\text{A}, V_{Ix} = V_{IxH}$           |

|                                                              |                                                                              | $V_{DD1} - 0.5$ , $V_{ISO} - 0.5$   | 4.8   |      | V     | $I_{Ox} = -4 \text{ mA}, V_{Ix} = V_{IxH}$               |

| Logic Low Output Voltages                                    | V <sub>OAL</sub> , V <sub>OBL</sub> ,<br>V <sub>OCL</sub> , V <sub>ODL</sub> |                                     | 0.0   | 0.1  | V     | $I_{Ox}=20~\mu\text{A, }V_{lx}=V_{lxL}$                  |

|                                                              |                                                                              |                                     | 0.0   | 0.4  | V     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$                |

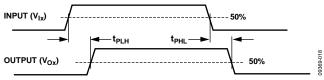

| AC SPECIFICATIONS                                            |                                                                              |                                     |       |      |       |                                                          |

| A Grade                                                      |                                                                              |                                     |       |      |       | $C_L = 15 \text{ pF, CMOS signal levels}$                |

| Minimum Pulse Width                                          | PW                                                                           |                                     |       | 1000 | ns    |                                                          |

| Maximum Data Rate                                            |                                                                              | 1                                   |       |      | Mbps  |                                                          |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub>                                          |                                     | 55    | 100  | ns    |                                                          |

| Pulse Width Distortion,  tplh - tphl                         | PWD                                                                          |                                     |       | 40   | ns    |                                                          |

| Propagation Delay Skew                                       | <b>t</b> <sub>PSK</sub>                                                      |                                     |       | 50   | ns    |                                                          |

| Channel-to-Channel Matching                                  | t <sub>PSKCD</sub> /t <sub>PSKOD</sub>                                       |                                     |       | 50   | ns    |                                                          |

| C Grade                                                      |                                                                              |                                     |       |      |       | $C_L = 15 \text{ pF, CMOS signal levels}$                |

| Minimum Pulse Width                                          | PW                                                                           |                                     |       | 40   | ns    |                                                          |

| Maximum Data Rate                                            |                                                                              | 25                                  |       |      | Mbps  |                                                          |

| Propagation Delay                                            | t <sub>PHL</sub> , t <sub>PLH</sub>                                          | 30                                  | 45    | 60   | ns    |                                                          |

| Pulse Width Distortion,  t <sub>PLH</sub> - t <sub>PHL</sub> | PWD                                                                          |                                     |       | 8    | ns    |                                                          |

| Change vs. Temperature                                       |                                                                              |                                     | 5     |      | ps/°C |                                                          |

| Propagation Delay Skew                                       | t <sub>PSK</sub>                                                             |                                     |       | 15   | ns    |                                                          |

| Channel-to-Channel Matching                                  |                                                                              |                                     |       |      |       |                                                          |

| Codirectional Channels                                       | t <sub>PSKCD</sub>                                                           |                                     |       | 8    | ns    |                                                          |

| Opposing Directional Channels                                | <b>t</b> PSKOD                                                               |                                     |       | 15   | ns    |                                                          |

| Output Rise/Fall Time (10% to 90%)                           | t <sub>R</sub> /t <sub>F</sub>                                               |                                     | 2.5   |      | ns    | C <sub>L</sub> = 15 pF, CMOS signal levels               |

| Common-Mode Transient Immunity                               |                                                                              |                                     |       |      |       | V <sub>CM</sub> = 1000 V, transient<br>magnitude = 800 V |

| At Logic High Output                                         | CM <sub>H</sub>                                                              | 25                                  | 35    |      | kV/μs | $V_{lx} = V_{DD1}$ or $V_{ISO}$                          |

| At Logic Low Output                                          | CML                                                                          | 25                                  | 35    |      | kV/μs | $V_{lx} = 0 V$                                           |

| Refresh Rate                                                 | f <sub>r</sub>                                                               |                                     | 1.0   |      | Mbps  |                                                          |

<sup>&</sup>lt;sup>1</sup> The contributions of supply current values for all four channels are combined at identical data rates.

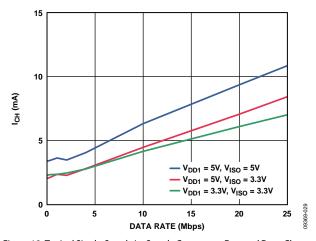

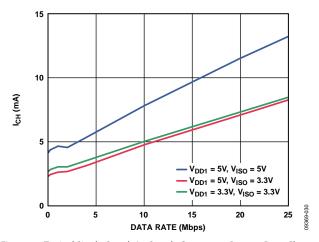

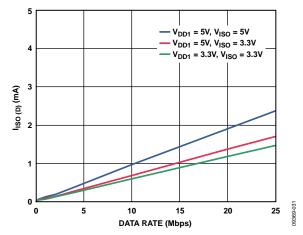

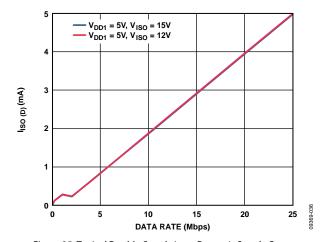

<sup>&</sup>lt;sup>2</sup> The V<sub>ISO</sub> supply current is available for external use when all data rates are below 2 Mbps. At data rates above 2 Mbps, the data I/O channels draw additional current proportional to the data rate. Additional supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. The dynamic I/O channel load must be treated as an external load and included in the V<sub>ISO</sub> power budget.

<sup>&</sup>lt;sup>3</sup> The power demands of the quiescent operation of the data channels is not separated from the power supply section. Efficiency includes the quiescent power consumed by the I/O channels as part of the internal power consumption.

<sup>&</sup>lt;sup>4</sup> This current is available for driving external loads at the V<sub>ISO</sub> output. All channels are simultaneously driven at a maximum data rate of 25 Mbps with full capacitive load representing the maximum dynamic load conditions. Refer to the Power Consumption section for calculation of the available current at less than the maximum data rate.

#### **ELECTRICAL CHARACTERISTICS—3.3 V PRIMARY INPUT SUPPLY/3.3 V SECONDARY ISOLATED SUPPLY**

$3.0~V \le V_{DD1} = V_{DDA} \le 3.6~V; V_{DD2} = V_{REG} = V_{ISO} = 3.3~V; f_{SW} = 500~kHz;$  all voltages are relative to their respective grounds (see the application schematic in Figure 38). All minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at  $T_A = 25^{\circ}C$ ,  $V_{DD1} = V_{DDA} = 3.3~V$ ,  $V_{DD2} = V_{REG} = V_{ISO} = 3.3~V$ .

Table 2.

| Parameter                                                             | Symbol                                                                | Min   | Тур   | Max   | Unit   | Test Conditions/Comments                                                                          |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|--------|---------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTER POWER SUPPLY                                       |                                                                       |       |       |       |        |                                                                                                   |

| Isolated Output Voltage                                               | V <sub>ISO</sub>                                                      | 3.0   | 3.3   | 3.6   | V      | $I_{ISO} = 0 \text{ mA}, V_{ISO} = V_{FB} \times (R1 + R2)/R2$                                    |

| Feedback Voltage Setpoint                                             | $V_{FB}$                                                              | 1.125 | 1.25  | 1.375 | V      | $I_{ISO} = 0 \text{ mA}$                                                                          |

| Line Regulation                                                       | V <sub>ISO (LINE)</sub>                                               |       | 1     | 10    | mV/V   | $I_{ISO} = 50 \text{ mA}, V_{DD1} = 3.0 \text{ V to } 3.6 \text{ V}$                              |

| Load Regulation                                                       | V <sub>ISO (LOAD)</sub>                                               |       | 1     | 2     | %      | $I_{ISO} = 20 \text{ mA to } 100 \text{ mA}$                                                      |

| Output Ripple                                                         | VISO (RIP)                                                            |       | 50    |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                   |

| Output Noise                                                          | V <sub>ISO (N)</sub>                                                  |       | 100   |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                   |

| Switching Frequency                                                   | $f_{SW}$                                                              |       | 1000  |       | kHz    | $R_{OC} = 50 \text{ k}\Omega$                                                                     |

|                                                                       |                                                                       |       | 200   |       | kHz    | $R_{OC} = 270 \text{ k}\Omega$                                                                    |

|                                                                       |                                                                       | 192   | 318   | 515   | kHz    | $V_{OC} = V_{DD2}$ (open loop)                                                                    |

| Switch On Resistance                                                  | Ron                                                                   |       | 0.6   |       | Ω      |                                                                                                   |

| Undervoltage Lockout, V <sub>DD1</sub> , V <sub>DD2</sub><br>Supplies |                                                                       |       |       |       |        |                                                                                                   |

| Positive Going Threshold                                              | $V_{\text{UV+}}$                                                      |       | 2.8   |       | V      |                                                                                                   |

| Negative Going Threshold                                              | $V_{UV-}$                                                             |       | 2.6   |       | V      |                                                                                                   |

| Hysteresis                                                            | V <sub>UVH</sub>                                                      |       | 0.2   |       | V      |                                                                                                   |

| DC to 2 Mbps Data Rate <sup>1</sup>                                   |                                                                       |       |       |       |        | f ≤ 1 MHz,                                                                                        |

| Maximum Output Supply Current <sup>2</sup>                            | I <sub>ISO (MAX)</sub>                                                | 250   |       |       | mA     | $V_{ISO} = 3.3 \text{ V}$                                                                         |

| Efficiency at Maximum Output<br>Supply Current <sup>3</sup>           |                                                                       |       | 70    |       | %      | $I_{ISO} = I_{ISO \ (MAX)}$                                                                       |

| <i>i</i> COUPLER DATA CHANNELS                                        |                                                                       |       |       |       |        |                                                                                                   |

| DC to 2 Mbps Data Rate <sup>1</sup>                                   |                                                                       |       |       |       |        |                                                                                                   |

| IDD1 Supply Current, No VISO Load                                     | I <sub>DD1 (Q)</sub>                                                  |       |       |       |        | $I_{ISO} = 0$ mA, $f \le 1$ MHz                                                                   |

| ADuM3470                                                              |                                                                       |       | 9     | 20    | mA     |                                                                                                   |

| ADuM3471                                                              |                                                                       |       | 10    | 20    | mA     |                                                                                                   |

| ADuM3472                                                              |                                                                       |       | 11    | 20    | mA     |                                                                                                   |

| ADuM3473                                                              |                                                                       |       | 11    | 20    | mA     |                                                                                                   |

| ADuM3474                                                              |                                                                       |       | 12    | 20    | mA     |                                                                                                   |

| 25 Mbps Data Rate (C Grade Only)                                      |                                                                       |       |       |       |        |                                                                                                   |

| IDD1 Supply Current, No VISO Load                                     | I <sub>DD1 (D)</sub>                                                  |       |       |       |        | $I_{ISO} = 0 \text{ mA}, C_L = 15 \text{ pF}, f = 12.5 \text{ MHz}$                               |

| ADuM3470                                                              |                                                                       |       | 28    |       | mA     |                                                                                                   |

| ADuM3471                                                              |                                                                       |       | 29    |       | mA     |                                                                                                   |

| ADuM3472                                                              |                                                                       |       | 31    |       | mA     |                                                                                                   |

| ADuM3473                                                              |                                                                       |       | 32    |       | mA     |                                                                                                   |

| ADuM3474                                                              |                                                                       |       | 34    |       | mA     |                                                                                                   |

| Available V <sub>ISO</sub> Supply Current <sup>4</sup>                | Iso (LOAD)                                                            |       |       |       |        | $C_L = 15 \text{ pF, } f = 12.5 \text{ MHz}$                                                      |

| ADuM3470                                                              |                                                                       |       | 244   |       | mA     |                                                                                                   |

| ADuM3471                                                              |                                                                       |       | 243   |       | mA     |                                                                                                   |

| ADuM3472                                                              |                                                                       |       | 241   |       | mA     |                                                                                                   |

| ADuM3473                                                              |                                                                       |       | 240   |       | mA     |                                                                                                   |

| ADuM3474                                                              |                                                                       |       | 238   |       | mA     |                                                                                                   |

| I <sub>DD1</sub> Supply Current, Full V <sub>ISO</sub> Load           | I <sub>DD1 (MAX)</sub>                                                |       | 350   |       | mA     | $C_L = 0 \text{ pF, } f = 0 \text{ MHz, } V_{DD1} = 3.3 \text{ V,}$<br>$I_{ISO} = 250 \text{ mA}$ |

| I/O Input Currents                                                    | I <sub>IA</sub> , I <sub>IB</sub> , I <sub>IC</sub> , I <sub>ID</sub> | -10   | +0.01 | +10   | μΑ     |                                                                                                   |

| Parameter                                     | Symbol                                                                       | Min                                 | Тур | Max  | Unit  | Test Conditions/Comments                                 |

|-----------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-----|------|-------|----------------------------------------------------------|

| Logic High Input Threshold                    | V <sub>IH</sub>                                                              | 1.6                                 |     |      | ٧     |                                                          |

| Logic Low Input Threshold                     | V <sub>IL</sub>                                                              |                                     |     | 0.4  | V     |                                                          |

| Logic High Output Voltages                    | V <sub>OAH</sub> , V <sub>OBH</sub> ,<br>V <sub>OCH</sub> , V <sub>ODH</sub> | $V_{DD1} - 0.3,$<br>$V_{ISO} - 0.3$ | 5.0 |      | V     | $I_{Ox} = -20 \mu A, V_{Ix} = V_{IxH}$                   |

|                                               |                                                                              | $V_{DD1} - 0.5,$<br>$V_{ISO} - 0.5$ | 4.8 |      | V     | $I_{Ox} = -4 \text{ mA, } V_{Ix} = V_{IxH}$              |

| Logic Low Output Voltages                     | V <sub>OAL</sub> , V <sub>OBL</sub> ,<br>V <sub>OCL</sub> , V <sub>ODL</sub> |                                     | 0.0 | 0.1  | V     | $I_{Ox}=20~\mu\text{A}, V_{Ix}=V_{IxL}$                  |

|                                               |                                                                              |                                     | 0.0 | 0.4  | V     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$                |

| AC SPECIFICATIONS                             |                                                                              |                                     |     |      |       |                                                          |

| A Grade                                       |                                                                              |                                     |     |      |       | $C_L = 15$ pF, CMOS signal levels                        |

| Minimum Pulse Width                           | PW                                                                           |                                     |     | 1000 | ns    |                                                          |

| Maximum Data Rate                             |                                                                              | 1                                   |     |      | Mbps  |                                                          |

| Propagation Delay                             | t <sub>PHL</sub> , t <sub>PLH</sub>                                          |                                     | 60  | 100  | ns    |                                                          |

| Pulse Width Distortion,  tplh - tphl          | PWD                                                                          |                                     |     | 40   | ns    |                                                          |

| Propagation Delay Skew                        | t <sub>PSK</sub>                                                             |                                     |     | 50   | ns    |                                                          |

| Channel-to-Channel Matching                   | t <sub>PSKCD</sub> /t <sub>PSKOD</sub>                                       |                                     |     | 50   | ns    |                                                          |

| C Grade                                       |                                                                              |                                     |     |      |       | $C_L = 15$ pF, CMOS signal levels                        |

| Minimum Pulse Width                           | PW                                                                           |                                     |     | 40   | ns    |                                                          |

| Maximum Data Rate                             |                                                                              | 25                                  |     |      | Mbps  |                                                          |

| Propagation Delay                             | t <sub>PHL</sub> , t <sub>PLH</sub>                                          | 30                                  | 60  | 75   | ns    |                                                          |

| Pulse Width Distortion, $ t_{PLH} - t_{PHL} $ | PWD                                                                          |                                     |     | 8    | ns    |                                                          |

| Change vs. Temperature                        |                                                                              |                                     | 5   |      | ps/°C |                                                          |

| Propagation Delay Skew                        | t <sub>PSK</sub>                                                             |                                     |     | 45   | ns    |                                                          |

| Channel-to-Channel Matching                   |                                                                              |                                     |     |      |       |                                                          |

| Codirectional Channels                        | <b>t</b> PSKCD                                                               |                                     |     | 8    | ns    |                                                          |

| Opposing Directional Channels                 | t <sub>PSKOD</sub>                                                           |                                     |     | 15   | ns    |                                                          |

| Output Rise/Fall Time (10% to 90%)            | t <sub>R</sub> /t <sub>F</sub>                                               |                                     | 2.5 |      | ns    | $C_L = 15$ pF, CMOS signal levels                        |

| Common-Mode Transient Immunity                |                                                                              |                                     |     |      |       | V <sub>CM</sub> = 1000 V, transient<br>magnitude = 800 V |

| At Logic High Output                          | CM <sub>H</sub>                                                              | 25                                  | 35  |      | kV/μs | $V_{Ix} = V_{DD1} \text{ or } V_{ISO}$                   |

| At Logic Low Output                           | CM <sub>L</sub>                                                              | 25                                  | 35  |      | kV/μs | $V_{lx} = 0 V$                                           |

| Refresh Rate                                  | f <sub>r</sub>                                                               |                                     | 1.0 |      | Mbps  |                                                          |

<sup>&</sup>lt;sup>1</sup> The contributions of supply current values for all four channels are combined at identical data rates.

<sup>&</sup>lt;sup>2</sup> The V<sub>ISO</sub> supply current is available for external use when all data rates are below 2 Mbps. At data rates above 2 Mbps, the data I/O channels draw additional current proportional to the data rate. Additional supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. The dynamic I/O channel load must be treated as an external load and included in the V<sub>ISO</sub> power budget.

<sup>&</sup>lt;sup>3</sup> The power demands of the quiescent operation of the data channels is not separated from the power supply section. Efficiency includes the quiescent power consumed by the I/O channels as part of the internal power consumption.

<sup>&</sup>lt;sup>4</sup> This current is available for driving external loads at the V<sub>ISO</sub> output. All channels are simultaneously driven at a maximum data rate of 25 Mbps with full capacitive load representing the maximum dynamic load conditions. Refer to the Power Consumption section for calculation of the available current at less than the maximum data rate.

#### ELECTRICAL CHARACTERISTICS—5 V PRIMARY INPUT SUPPLY/3.3 V SECONDARY ISOLATED SUPPLY

$4.5~V \le V_{DD1} = V_{DDA} \le 5.5~V; V_{DD2} = V_{REG} = V_{ISO} = 3.3~V; f_{SW} = 500~kHz;$  all voltages are relative to their respective grounds (see the application schematic in Figure 38). All minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at  $T_A = 25^{\circ}C$ ,  $V_{DD1} = V_{DDA} = 5.0~V$ ,  $V_{DD2} = V_{REG} = V_{ISO} = 3.3~V$ .

Table 3.

| Parameter                                                             | Symbol                                                                | Min   | Тур   | Max   | Unit   | Test Conditions/Comments                                                                        |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|--------|-------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTER POWER SUPPLY                                       |                                                                       |       |       |       |        |                                                                                                 |

| Isolated Output Voltage                                               | V <sub>ISO</sub>                                                      | 3.0   | 3.3   | 3.6   | ٧      | $I_{ISO} = 0 \text{ mA}, V_{ISO} = V_{FB} \times (R1 + R2)/R2$                                  |

| Feedback Voltage Setpoint                                             | $V_{FB}$                                                              | 1.125 | 1.25  | 1.375 | V      | $I_{ISO} = 0 \text{ mA}$                                                                        |

| Line Regulation                                                       | V <sub>ISO (LINE)</sub>                                               |       | 1     | 10    | mV/V   | $I_{ISO} = 50 \text{ mA}, V_{DD1} = 4.5 \text{ V to } 5.5 \text{ V}$                            |

| Load Regulation                                                       | V <sub>ISO</sub> (LOAD)                                               |       | 1     | 2     | %      | I <sub>ISO</sub> = 50 mA to 200 mA                                                              |

| Output Ripple                                                         | V <sub>ISO</sub> (RIP)                                                |       | 50    |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                 |

| Output Noise                                                          | V <sub>ISO (N)</sub>                                                  |       | 100   |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                 |

| Switching Frequency                                                   | $f_{SW}$                                                              |       | 1000  |       | kHz    | $R_{OC} = 50 \text{ k}\Omega$                                                                   |

|                                                                       |                                                                       |       | 200   |       | kHz    | $R_{OC} = 270 \text{ k}\Omega$                                                                  |

|                                                                       |                                                                       | 192   | 318   | 515   | kHz    | $V_{OC} = V_{DD2}$ (open loop)                                                                  |

| Switch On Resistance                                                  | Ron                                                                   |       | 0.5   |       | Ω      |                                                                                                 |

| Undervoltage Lockout, V <sub>DD1</sub> , V <sub>DD2</sub><br>Supplies |                                                                       |       |       |       |        |                                                                                                 |

| Positive Going Threshold                                              | $V_{\text{UV+}}$                                                      |       | 2.8   |       | V      |                                                                                                 |

| Negative Going Threshold                                              | $V_{\text{UV}-}$                                                      |       | 2.6   |       | V      |                                                                                                 |

| Hysteresis                                                            | $V_{UVH}$                                                             |       | 0.2   |       | V      |                                                                                                 |

| DC to 2 Mbps Data Rate <sup>1</sup>                                   |                                                                       |       |       |       |        | f≤1 MHz                                                                                         |

| Maximum Output Supply Current <sup>2</sup>                            | I <sub>ISO (MAX)</sub>                                                | 400   |       |       | mA     | $V_{ISO} = 3.3 \text{ V}$                                                                       |

| Efficiency at Maximum Output<br>Supply Current <sup>3</sup>           |                                                                       |       | 70    |       | %      | $I_{ISO} = I_{ISO (MAX)}$                                                                       |

| <i>i</i> COUPLER DATA CHANNELS                                        |                                                                       |       |       |       |        |                                                                                                 |

| DC to 2 Mbps Data Rate <sup>1</sup>                                   |                                                                       |       |       |       |        |                                                                                                 |

| $I_{DD1}$ Supply Current, No $V_{ISO}$ Load                           | I <sub>DD1 (Q)</sub>                                                  |       |       |       |        | $I_{ISO} = 0$ mA, $f \le 1$ MHz                                                                 |

| ADuM3470                                                              |                                                                       |       | 9     | 30    | mA     |                                                                                                 |

| ADuM3471                                                              |                                                                       |       | 9     | 30    | mA     |                                                                                                 |

| ADuM3472                                                              |                                                                       |       | 10    | 30    | mA     |                                                                                                 |

| ADuM3473                                                              |                                                                       |       | 10    | 30    | mA     |                                                                                                 |

| ADuM3474                                                              |                                                                       |       | 10    | 30    | mA     |                                                                                                 |

| 25 Mbps Data Rate (C Grade Only)                                      |                                                                       |       |       |       |        |                                                                                                 |

| IDD1 Supply Current, No VISO Load                                     | I <sub>DD1 (D)</sub>                                                  |       |       |       |        | $I_{ISO} = 0 \text{ mA}, C_L = 15 \text{ pF}, f = 12.5 \text{ MHz}$                             |

| ADuM3470                                                              |                                                                       |       | 33    |       | mA     |                                                                                                 |

| ADuM3471                                                              |                                                                       |       | 33    |       | mA     |                                                                                                 |

| ADuM3472                                                              |                                                                       |       | 33    |       | mA     |                                                                                                 |

| ADuM3473                                                              |                                                                       |       | 33    |       | mA     |                                                                                                 |

| ADuM3474                                                              |                                                                       |       | 33    |       | mA     |                                                                                                 |

| Available V <sub>ISO</sub> Supply Current <sup>4</sup>                | Iso (load)                                                            |       |       |       |        | $C_L = 15 \text{ pF, f} = 12.5 \text{ MHz}$                                                     |

| ADuM3470                                                              |                                                                       |       | 393   |       | mA     |                                                                                                 |

| ADuM3471                                                              |                                                                       |       | 392   |       | mA     |                                                                                                 |

| ADuM3472                                                              |                                                                       |       | 390   |       | mA     |                                                                                                 |

| ADuM3473                                                              |                                                                       |       | 389   |       | mA     |                                                                                                 |

| ADuM3474                                                              | 1.                                                                    |       | 388   |       | mA     |                                                                                                 |

| I <sub>DD1</sub> Supply Current, Full V <sub>ISO</sub> Load           | I <sub>DD1</sub> (MAX)                                                |       | 375   | _     | mA     | $C_L = 0 \text{ pF, } f = 0 \text{ MHz, } V_{DD1} = 5 \text{ V,}$<br>$I_{ISO} = 400 \text{ mA}$ |

| I/O Input Currents                                                    | I <sub>IA</sub> , I <sub>IB</sub> , I <sub>IC</sub> , I <sub>ID</sub> | -20   | +0.01 | +20   | μΑ     |                                                                                                 |

| Parameter                             | Symbol                                                                       | Min                                 | Тур | Max  | Unit  | Test Conditions/Comments                                 |

|---------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-----|------|-------|----------------------------------------------------------|

| Logic High Input Threshold            | V <sub>IH</sub>                                                              | 2.0                                 |     |      | ٧     |                                                          |

| Logic Low Input Threshold             | VIL                                                                          |                                     |     | 8.0  | V     |                                                          |

| Logic High Output Voltages            | Voah, Vobh,<br>Voch, Vodh                                                    | $V_{DD1} - 0.3,$<br>$V_{ISO} - 0.3$ | 5.0 |      | V     | $I_{Ox} = -20 \mu A, V_{Ix} = V_{IxH}$                   |

|                                       |                                                                              | $V_{DD1} - 0.5$ , $V_{ISO} - 0.5$   | 4.8 |      | V     | $I_{Ox} = -4 \text{ mA, } V_{Ix} = V_{IxH}$              |

| Logic Low Output Voltages             | V <sub>OAL</sub> , V <sub>OBL</sub> ,<br>V <sub>OCL</sub> , V <sub>ODL</sub> |                                     | 0.0 | 0.1  | V     | $I_{Ox} = 20 \mu A$ , $V_{Ix} = V_{IxL}$                 |

|                                       |                                                                              |                                     | 0.0 | 0.4  | V     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$                |

| AC SPECIFICATIONS                     |                                                                              |                                     |     |      |       |                                                          |

| A Grade                               |                                                                              |                                     |     |      |       | $C_L = 15$ pF, CMOS signal levels                        |

| Minimum Pulse Width                   | PW                                                                           |                                     |     | 1000 | ns    |                                                          |

| Maximum Data Rate                     |                                                                              | 1                                   |     |      | Mbps  |                                                          |

| Propagation Delay                     | t <sub>PHL</sub> , t <sub>PLH</sub>                                          |                                     | 55  | 100  | ns    |                                                          |

| Pulse Width Distortion,   tplh - tphl | PWD                                                                          |                                     |     | 40   | ns    |                                                          |

| Propagation Delay Skew                | t <sub>PSK</sub>                                                             |                                     |     | 50   | ns    |                                                          |

| Channel-to-Channel Matching           | t <sub>PSKCD</sub> /t <sub>PSKOD</sub>                                       |                                     |     | 50   | ns    |                                                          |

| C Grade                               |                                                                              |                                     |     |      |       | $C_L = 15$ pF, CMOS signal levels                        |

| Minimum Pulse Width                   | PW                                                                           |                                     |     | 40   | ns    |                                                          |

| Maximum Data Rate                     |                                                                              | 25                                  |     |      | Mbps  |                                                          |

| Propagation Delay                     | t <sub>PHL</sub> , t <sub>PLH</sub>                                          | 30                                  | 50  | 70   | ns    |                                                          |

| Pulse Width Distortion,   tplh - tphl | PWD                                                                          |                                     |     | 8    | ns    |                                                          |

| Change vs. Temperature                |                                                                              |                                     | 5   |      | ps/°C |                                                          |

| Propagation Delay Skew                | t <sub>PSK</sub>                                                             |                                     |     | 15   | ns    |                                                          |

| Channel-to-Channel Matching           |                                                                              |                                     |     |      |       |                                                          |

| Codirectional Channels                | <b>t</b> <sub>PSKCD</sub>                                                    |                                     |     | 8    | ns    |                                                          |

| Opposing Directional Channels         | t <sub>PSKOD</sub>                                                           |                                     |     | 15   | ns    |                                                          |

| Output Rise/Fall Time (10% to 90%)    | t <sub>R</sub> /t <sub>F</sub>                                               |                                     | 2.5 |      | ns    | C <sub>L</sub> = 15 pF, CMOS signal levels               |

| Common-Mode Transient Immunity        |                                                                              |                                     |     |      |       | V <sub>CM</sub> = 1000 V, transient<br>magnitude = 800 V |

| At Logic High Output                  | CM <sub>H</sub>                                                              | 25                                  | 35  |      | kV/μs | $V_{Ix} = V_{DD1} \text{ or } V_{ISO}$                   |

| At Logic Low Output                   | CM∟                                                                          | 25                                  | 35  |      | kV/μs | $V_{lx} = 0 V$                                           |

| Refresh Rate                          | fr                                                                           |                                     | 1.0 |      | Mbps  |                                                          |

<sup>&</sup>lt;sup>1</sup> The contributions of supply current values for all four channels are combined at identical data rates.

<sup>&</sup>lt;sup>2</sup> The V<sub>ISO</sub> supply current is available for external use when all data rates are below 2 Mbps. At data rates above 2 Mbps, the data I/O channels draw additional current proportional to the data rate. Additional supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. The dynamic I/O channel load must be treated as an external load and included in the V<sub>ISO</sub> power budget.

<sup>&</sup>lt;sup>3</sup> The power demands of the quiescent operation of the data channels is not separated from the power supply section. Efficiency includes the quiescent power consumed by the I/O channels as part of the internal power consumption.

<sup>&</sup>lt;sup>4</sup> This current is available for driving external loads at the V<sub>ISO</sub> output. All channels are simultaneously driven at a maximum data rate of 25 Mbps with full capacitive load representing the maximum dynamic load conditions. Refer to the Power Consumption section for calculation of the available current at less than the maximum data rate.

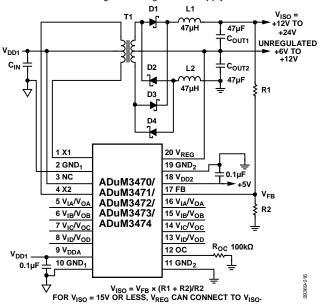

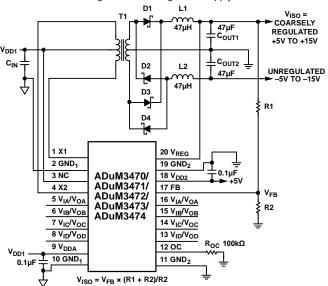

#### ELECTRICAL CHARACTERISTICS—5 V PRIMARY INPUT SUPPLY/15 V SECONDARY ISOLATED SUPPLY

$4.5 \text{ V} \le V_{DD1} = V_{DDA} \le 5.5 \text{ V}; V_{REG} = V_{ISO} = 15 \text{ V}; V_{DD2} = 5.0 \text{ V}; f_{SW} = 500 \text{ kHz}; all voltages are relative to their respective grounds (see the application schematic in Figure 39). All minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at <math>T_A = 25^{\circ}\text{C}, V_{DD1} = V_{DDA} = 5.0 \text{ V}, V_{REG} = V_{ISO} = 15 \text{ V}, V_{DD2} = 5.0 \text{ V}.$

Table 4.

| Parameter                                                          | Symbol                  | Min   | Тур  | Max   | Unit   | Test Conditions/Comments                                                                        |

|--------------------------------------------------------------------|-------------------------|-------|------|-------|--------|-------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTER POWER SUPPLY                                    |                         |       | •    |       |        |                                                                                                 |

| Isolated Output Voltage                                            | V <sub>ISO</sub>        | 13.5  | 15   | 16.5  | V      | $I_{ISO} = 0 \text{ mA}, V_{ISO} = V_{FB} \times (R1 + R2)/R2$                                  |

| Feedback Voltage Setpoint                                          | $V_{FB}$                | 1.125 | 1.25 | 1.375 | V      | $I_{ISO} = 0 \text{ mA}$                                                                        |

| V <sub>DD2</sub> Linear Regulator                                  |                         |       |      |       |        |                                                                                                 |

| Regulator Voltage                                                  | $V_{DD2}$               | 4.6   | 5.0  | 5.7   | V      | $V_{REG} = 7 \text{ V to } 15 \text{ V, } I_{DD2} = 0 \text{ mA}$ to 50 mA                      |

| Dropout Voltage                                                    | V <sub>DD2 (DO)</sub>   |       | 0.5  | 1.5   | V      | $I_{DD2} = 50 \text{ mA}$                                                                       |

| Line Regulation                                                    | V <sub>ISO (LINE)</sub> |       | 1    | 20    | mV/V   | $I_{ISO} = 50 \text{ mA}, V_{DD1} = 4.5 \text{ V to } 5.5 \text{ V}$                            |

| Load Regulation                                                    | V <sub>ISO (LOAD)</sub> |       | 1    | 3     | %      | $I_{ISO} = 20 \text{ mA to } 100 \text{ mA}$                                                    |

| Output Ripple                                                      | V <sub>ISO (RIP)</sub>  |       | 200  |       | mV p-p | 20 MHz bandwidth,<br>$C_{OUT} = 0.1 \mu F   47 \mu F, I_{ISO} = 100 \text{ mA}$                 |

| Output Noise                                                       | V <sub>ISO (N)</sub>    |       | 500  |       | mV p-p | 20 MHz bandwidth,<br>C <sub>OUT</sub> = 0.1 μF  47 μF, I <sub>ISO</sub> = 100 mA                |

| Switching Frequency                                                | $f_{SW}$                |       | 1000 |       | kHz    | $R_{OC} = 50 \text{ k}\Omega$                                                                   |

|                                                                    |                         |       | 200  |       | kHz    | $R_{OC} = 270 \text{ k}\Omega$                                                                  |

|                                                                    |                         | 192   | 318  | 515   | kHz    | $V_{OC} = V_{DD2}$ (open loop)                                                                  |

| Switch On Resistance                                               | Ron                     |       | 0.5  |       | Ω      |                                                                                                 |

| Undervoltage Lockout, V <sub>DD1</sub> , V <sub>DD2</sub> Supplies |                         |       |      |       |        |                                                                                                 |

| Positive Going Threshold                                           | $V_{UV+}$               |       | 2.8  |       | V      |                                                                                                 |

| Negative Going Threshold                                           | $V_{UV-}$               |       | 2.6  |       | V      |                                                                                                 |

| Hysteresis                                                         | V <sub>UVH</sub>        |       | 0.2  |       | V      |                                                                                                 |

| DC to 2 Mbps Data Rate <sup>1</sup>                                | 2111                    |       |      |       |        | f≤1 MHz                                                                                         |

| Maximum Output Supply Current <sup>2</sup>                         | I <sub>ISO (MAX)</sub>  | 100   |      |       | mA     | $V_{ISO} = 5.0 \text{ V}$                                                                       |

| Efficiency at Maximum Output                                       |                         |       | 70   |       | %      | $I_{ISO} = I_{ISO (MAX)}$                                                                       |

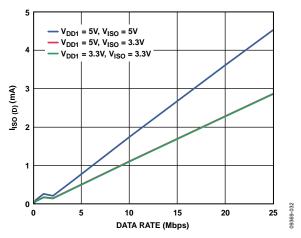

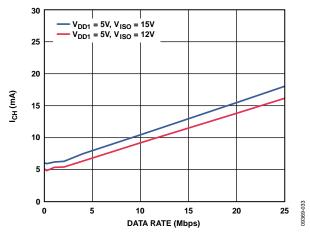

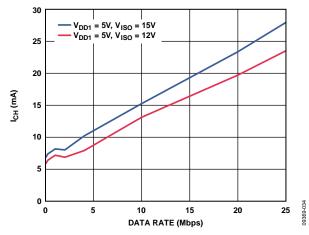

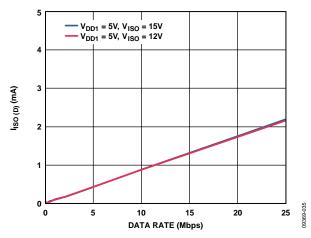

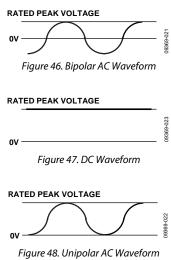

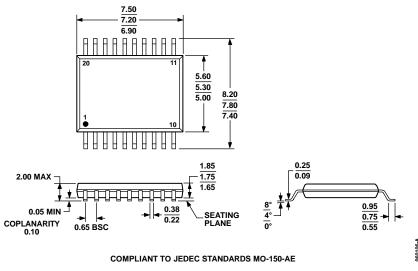

| Supply Current <sup>3</sup>                                        |                         |       |      |       | ,,,    | 150 150 (1110)                                                                                  |