## XRT94L31

#### 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC

MARCH 2007 REV. 1.0.1

#### GENERAL DESCRIPTION

The XRT94L31 is a highly integrated SONET/SDH terminator designed for E3/DS3/STS-1 mapping/demapping functions from either the STS-3 or STM-1 data stream. The XRT94L31 interfaces directly to the optical transceiver.

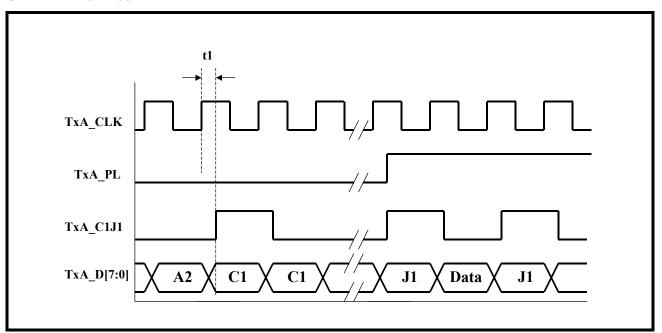

The XRT94L31 processes the section, line and path overhead in the SONET/SDH data stream. The processing of path overhead bytes within the STS-1s or TUG-3s includes 64 bytes for storing the J1 bytes. Path overhead bytes can be accessed through the microprocessor interface or via serial interface.

The XRT94L31 uses the internal E3/DS3 De-Synchronizer circuit with an internal pointer leak algorithm for clock smoothing as well as to remove the jitter due to mapping and pointer movements. These De-Synchronizer circuits do not need any external clock reference for its operation.

The SONET/SDH transmit blocks allow flexible insertion of TOH and POH bytes through both Hardware and Software. Individual POH bytes for the transmitted SONET/SDH signal are mapped either from the XRT94L31 memory map or from external interface. A1, A2 framing pattern, C1 byte and H1, H2 pointer byte are generated.

The SONET/SDH receive blocks receive SONET STS-3 signal or SDH STM-1 signal and perform the necessary transport and path overhead processing.

The XRT94L31 provides a line side APS (Automatic Protection Switching) interface by offering redundant receive serial interface to be switched at the frame boundary.

The XRT94L31 provides 3 mappers for performing STS-1/VC-3 to STS-1/DS3/E3 mapping function, one for each STS-1/DS3/E3 framers.

A PRBS test pattern generation and detection is implemented to measure the bit-error performance.

A general-purpose microprocessor interface is included for control, configuration and monitoring.

#### **APPLICATIONS**

- Network switches

- Add/Drop Multiplexer

- W-DCS Digital Cross Connect Systems

#### **FEATURES**

- Provides DS3/ E3 mapping/de-mapping for up to 3 tributaries through SONET STS-1 or SDH AU-3 and/or TUG-3/AU-4 containers

- Generates and terminates SONET/SDH section, line and path layers

- Integrated SERDES with Clock Recovery Circuit

- Provides SONET frame scrambling and descrambling

- Integrated Clock Synthesizer that generates 155 MHz and 77.76 MHz clock from an external 12.96/ 19.44/77.76 MHz reference clock

- Integrated 3 E3/DS3/STS-1 De-Synchronizer circuit that de-jitter gapped clock to meet 0.05Ulpp jitter requirements

- Access to Line or Section DCC

- Level 2 Performance Monitoring for E3 and DS3

- Supports mixing of STS-1E and DS3 or E3 and DS3 tributaries

- E3 and DS3 framers for both Transmit and Receive directions

- Complete Transport/Section Overhead Processing and generation per Telcordia and ITU standards

- Single PHY and Multi-PHY operations supported

- Full line APS support for redundancy applications

- Loopback support for both SONET/SDH as well as E3/DS3/STS-1

- Boundary scan capability with JTAG IEEE 1149-8bit microprocessor interface-

- 3.3 V ± 5% Power Supply; 5 V input signal tolerance

- -40°C to +85°C Operating Temperature Range

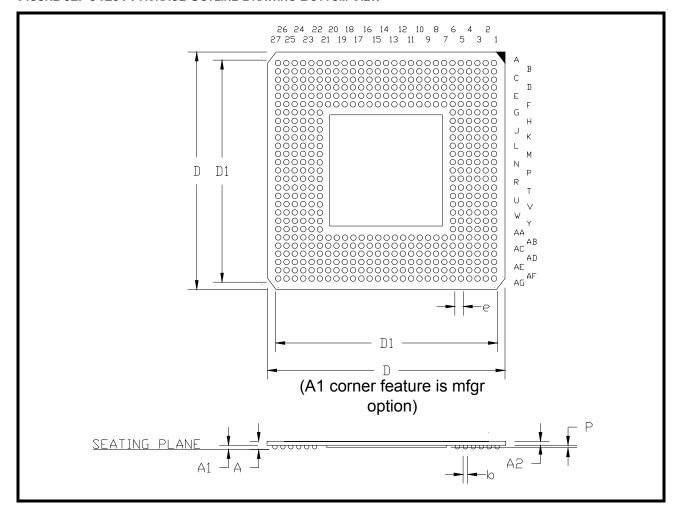

- Available in a 504 Ball TBGA package

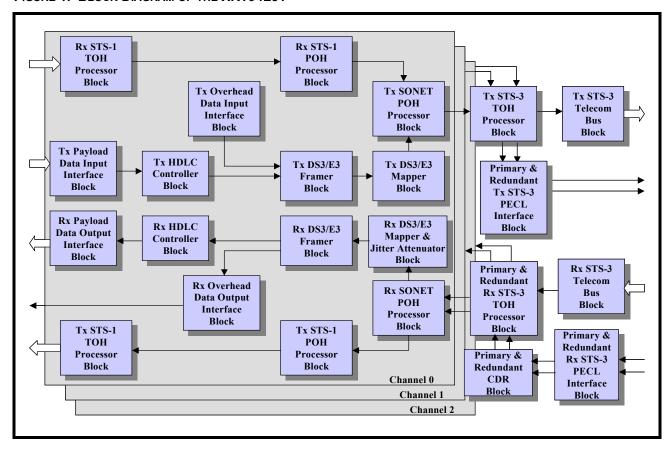

#### FIGURE 1. BLOCK DIAGRAM OF THE XRT94L31

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE          | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------|-----------------------------|

| XRT94L31IB  | 27 x 27 504 Lead TBGA | -40°C to +85°C              |

| PIN#                                                                                                              | SIGNAL NAME                                                                                                                                    | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                   |                                                                                                                                                |     | MIC  | ROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

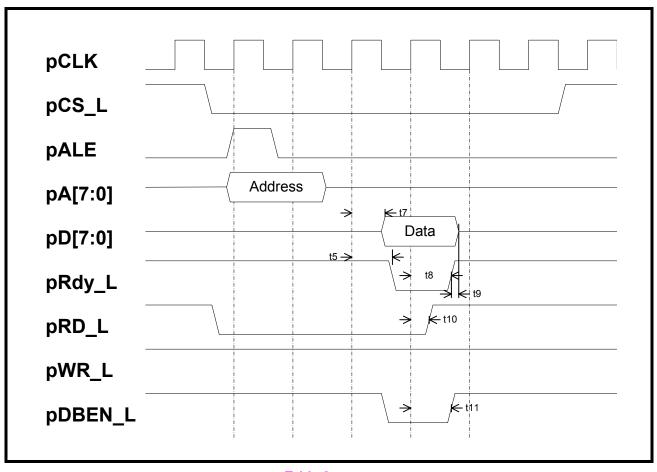

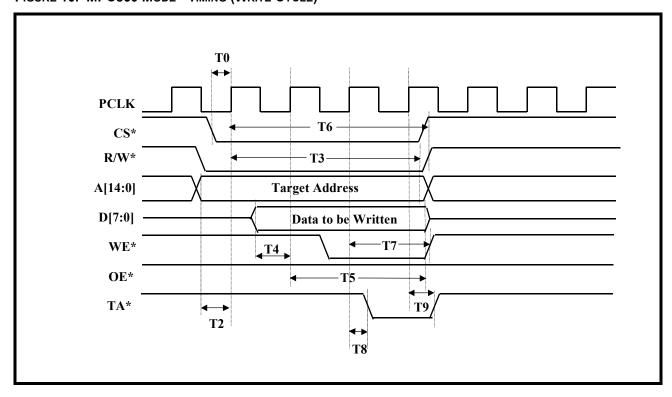

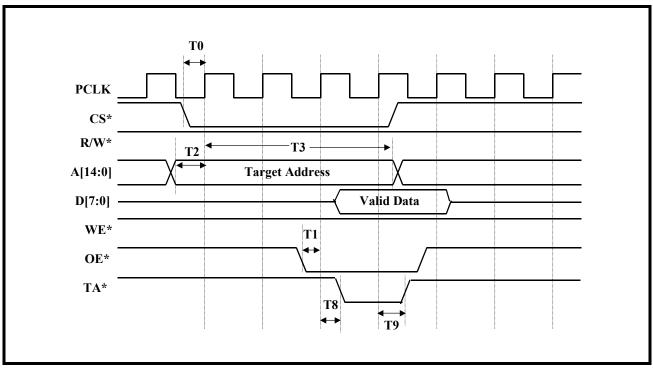

| Y22                                                                                                               | PCLK                                                                                                                                           | _   | TTL  | <ul> <li>Microprocessor Interface Clock Input: This clock input signal is only used if the Microprocessor Interface has been configured to operate in one of the Synchronous Modes (e.g., Power PC 403 Mode). If the Microprocessor Interface is configured to operate in one of these modes, then it will use this clock signal to do the following. </li> <li>To sample the CS*, WR*/R/W*, A[14:0], D[7:0], RD*/DS* and DBEN input pins, and To update the state of D[7:0] and the RDY/DTACK output signals.</li> <li>Notes: <ol> <li>The Microprocessor Interface can work with mPCLK frequencies ranging up to 33MHz.</li> <li>This pin is inactive if the Microprocessor Interface has been configured to operate in either the Intel-Asynchronous or the Motorola-Asynchronousl Modes. In this case, tie this pin to GND.</li> </ol> </li> </ul> |

| AD25<br>AD23<br>AC21                                                                                              | PTYPE_0PTYPE_1P<br>TYPE_2                                                                                                                      | _   | TTL  | Microprocessor Type Select input:  These three input pins are used to configure the Microprocessor Interface block to readily support a wide variety of Microprocessor Interfaces. The relationship between the settings of these input pins and the corresponding Microprocessor Interface configuration is presented below.  PTYPE[2:0] Microprocessor Interface Mode  000 Intel-Asynchronous Mode  001 Motorola - Asynchronous Mode  010 Intel X86  011 Intel I960  100 IDT3051/52 (MIPS)  101 Power PC 403 Mode  111 Motorola 860                                                                                                                                                                                                                                                                                                                  |

| AD27<br>AB25<br>W23<br>Y24<br>AD26<br>AC25<br>AA24<br>Y23<br>AE24<br>AB20<br>AD22<br>AC20<br>AD21<br>AE23<br>AF24 | PADDR_0 PADDR_1 PADDR_2 PADDR_3 PADDR_4 PADDR_5 PADDR_6 PADDR_7 PADDR_8 PADDR_9 PADDR_10 PADDR_11 PADDR_12 PADDR_12 PADDR_13 PADDR_13 PADDR_14 | ı   | TTL  | Address Bus Input pins (Microprocessor Interface): These pins permit the Microprocessor to identify on-chip registers and Buffer/Memory locations (within the XRT94L31) whenever it performs READ and WRITE operations with the XRT94L31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Experience Our Connectivity. REV. 1.0.1

| PIN#                                                         | SIGNAL NAME                                                     | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------|-----------------------------------------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD20<br>AC19<br>AE22<br>AG24<br>AE21<br>AD19<br>AF23<br>AE20 | PDATA_0 PDATA_1 PDATA_2 PDATA_3 PDATA_4 PDATA_5 PDATA_6 PDATA_7 | I/O | TTL  | Bi-Directional Data Bus pins (Microprocessor Interface): These pins are used to drive and receive data over the bi-directional data bus, whenever the Microprocessor performs READ and WRITE operations with the Microprocessor Interface of the XRT94L31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AF22                                                         | PWR_L/R/W*                                                      | I   | TTL  | Write Strobe/Read-Write Operation Identifier:  The function of this input pin depends upon which mode the Microprocessor Interface has been configured to operate in, as described below. Intel-Asynchronous Mode - WR* - Write Strobe Input:  If the Microprocessor Interface is configured to operate in the Intel-Asynchronous Mode, then this input pin functions as the WR* (Active-Low WRITE Strobe) input signal from the Microprocessor. Once this active-low signal is asserted, then the input buffers (associated with the Bi-Directional Data Bus pins, D[7:0]) will be enabled. The Microprocessor Interface will latch the contents on the Bi-Directional Data Bus (into the target register or address location, within the XRT94L31) upon the rising of this input.  Motorola-Asynchronous Mode - R/W* - Read/Write Operation Identification Input Pin:  If the Microprocessor Interface is operating in the Motorola-Asynchronous Mode, then this pin is functionally equivalent to the R/W* input pin. In the Motorola Mode, a READ operation occurs if this pin is held at a logic 1, coincident to a falling edge of the RD/DS* (Data Strobe) input pin.  PowerPC 403 Mode - R/W* - Read/Write Operation Identification Input:  If the Microprocessor Interface is configured to operate in the PowerPC 403 Mode, then this input pin will function as the Read/Write Operation Identification input pin.  Anytime the Microprocessor Interface samples this input signal at a logic "Low" (while also sampling the CS* input pin "Low") upon the rising edge of PCLK, then the Microprocessor Interface will (upon the very same rising edge of PCLK) latch the contents of the Address Bus (A]14:0]) into the Microprocessor Interface circuitry, in preparation for this forthcoming READ operation. At some point (later in this READ operation) the Microprocessor Interface will then place the contents of the target register (or address location within the XRT94L31) upon the Bi-Directional Dat Bus pins (D[7:0]), where it can be read by the Microprocessor.  Anytime the Microprocessor Int |

|                                                              |                                                                 |     |      | "High" (while also sampling the CS* input pin at a logic "Low") upon the rising edge of PCLK, then the Microprocessor Interface will (upon the very same rising edge of PCLK) latch the contents of the Address Bus (A[14:0]) into the Microprocessor Interface circuitry, in preparation for the forthcoming WRITE operation. At some point (later in this WRITE operation) the Microprocessor will also assert the RD*/DS*/WE* input pin, and the Microprocessor Interface will then latch the contents of the Bi-Directional Data Bus (D[7:0]) into the contents of the target register or buffer location (within the XRT94L31).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIN# | SIGNAL NAME   | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC18 | PRD_L/DS*/WE* | I   | TTL  | READ Strobe /Data Strobe:  The function of this input pin depends upon which mode the Microprocessor Interface has been configured to operate in, as described below.  Intel-Asynchronous Mode - RD* - READ Strobe Input:  If the Microprocessor Interface is operating in the Intel-Asynchronous Mode, then this input pin will function as the RD* (Active "Low" READ Strobe) input signal from the Microprocessor. Once this active-low signal is asserted, then the XRT94L31 will place the contents of the addressed register (or buffer location) on the Microprocessor Bi-directional Data Bus (D[7:0]). When this signal is negated, the Data Bus will be tri-stated.  Motorola-Asynchronous (68K) Mode - DS* - Data Strobe Input:  If the Microprocessor Interface is operating in the Motorola Asynchronous Mode, then this input will function as the DS* (Data Strobe) input signal.  PowerPC 403 Mode - WE* - Write Enable Input:  If the Microprocessor Interface is operating in the PowerPC 403 Mode, then this input pin will function as the WE* (Write Enable) input pin.  Anytime the Microprocessor Interface samples this active-low input signal (along with CS* and WR*/R/W*) also being asserted (at a logic level) upon the rising edge of PCLK, then the Microprocessor Interface will (upon the very same rising edge of PCLK) latch the contents on the Bi-Directional Data Bus (D[7:0]) into the target on-chip register or buffer location within the XRT94L31.                                                                                            |

| AG23 | ALE/AS_L      | 1   | TTL  | Address Latch Enable/Address Strobe:T he function of this input pin depends upon which mode the Microprocessor Interface has been configured to operate in, as described below.  Intel-Asynchronous Mode - ALE  If the Microprocessor Interface (of the XRT94L31) has been configured to operate in the Intel-Asynchronous Mode, then this active-high input pin is used to latch the address (present at the Microprocessor Interface Address Bus input pins (A[14:0]) into the XRT94L31 Microprocessor Interface block and to indicate the start of a READ or WRITE cycle. Pulling this input pin "High" enables the input bus drivers for the Address Bus input pins (A[14:0]). The contents of the Address Bus will be latched into the XRT94L31 Microprocessor Interface circuitry, upon the falling edge of this input signal.  Motorola-Asynchronous (68K) Mode - AS*  If the Microprocessor Interface has been configured to operate in the Motorola-Asynchronous Mode, then this active-low input pin is used to latch the data (residing on the Address Bus, A[14:0]) into the Microprocessor Interface circuitry of the XRT94L31.  Pulling this input pin "Low" enables the input bus drivers for the Address Bus input pins. The contents of the Address Bus will be latched into the Microprocessor Interface circuitry, upon the rising edge of this signal.  PowerPC 403 Mode - No Function - Tie to GND:  If the MIcroprocessor Interface has been configured to operate in the PowerPC 403 Mode, then this input pin has no role nor function and should be tied to GND. |

| PIN# | SIGNAL NAME          | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|----------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE19 | PCS_L                | I   | TTL  | Chip Select Input: This active-low signal must be asserted in order to select the Microprocessor Interface for READ and WRITE operations between the Microprocessor and the XRT94L31 on-chip registers, LAPD and Trace Buffer locations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AD18 | PRDY_L/<br>DTACK*RDY | 0   | CMOS | READY or DTACK Output:  The function of this input pin depends upon wich mode the Microprocessor Interface has been configured to operate in, as described below.  Intel Asynchronous Mode - RDY* - READY output:  If the Microprocessor Interface has been configured to operate in the Intel-Asynchronous Mode, then this output pin will function as the active-low READY output.  During a READ or WRITE cycle, the Microprocessor Interface block will toggle this output pin to the logic "Low" level ONLY when it (the Microprocessor Interface) is ready to complete or terminate the current READ or WRITE cycle. Once the Microprocessor has determined that this input pin has toggled to the logic "Low" level, then it is now safe for it to move on and execute the next READ or WRITE cycle.  If (during a READ or WRITE cycle) the Microprocessor Interface block is holding this output pin at a logic "High" level, then the Microprocessor is expected to extend this READ or WRITE cycle, until it detect this output pin being toggled to the logic "Low" level.  Motorola Mode - DTACK* - Data Transfer Acknowledge Output:  If the Microprocessor Interface has been configured to operate in the Motorola-Asynchronous Mode, then this output pin will function as the active-low DTACK* output.  During a READ or WRITE cycle, the Microprocessor Interface block will toggle this output pin to the logic "Low" level, ONLY when it (the Microprocessor Interface) is ready to complete or terminate the current READ or WRITE cycle. Once the Microprocessor has determined that this input pin has toggled to the logic "Low" level, then it is now safe for it to move on and execute the next READ or WRITE cycle, until it detects this output pin being toggled to the logic "High" level, then the Microprocessor is expected to extend this READ or WRITE cycle, until it detects this output pin being toggled to the logic "High" level, When the Microprocessor Interface block will toggle this output pin to the logic "High" level, ONLY when the Microprocessor Interface is ready to |

| PIN# | SIGNAL NAME    | I/O | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AF21 | PDBEN_L        | I   | TTL        | Bi-directional Data Bus Enable Input pin:  This input pin is used to either enable or tri-state the Bi-Directional Data Bus pins (D[7:0]), as described below.  Setting this input pin "Low" enables the Bi-directional Data bus.  Setting this input "High" tri-states the Bi-directional Data Bus.                                                                                                                                                                                                      |

| AF20 | PBLAST_L       | ı   | TTL        | Last Burst Transfer Indicator input pin:  If the Microprocessor Interface is operating in the Intel-I960 Mode, then this input pin is used to indicate (to the Microprocessor Interface block) that the current data transfer is the last data transfer within the current burst operation.  The Microprocessor should assert this input pin (by toggling it "Low") in order to denote that the current READ or WRITE operation (within a BURST operation) is the last operation of this BURST operation. |

|      |                |     |            | <b>Note:</b> Connect this input pin to GND whenever the Microprocessor Interface has been configured to operate in the Intel-Async, Motorola 68K and IBM PowerPC 403 modes.                                                                                                                                                                                                                                                                                                                               |

| AG22 | PINT_L         | 0   | CMOS       | Interrupt Request Output:  This open-drain, active-low output signal will be asserted when the Mapper/Framer device is requesting interrupt service from the Microprocessor. This output pin should typically be connected to the Interrupt Request input of the Microprocessor.                                                                                                                                                                                                                          |

| AB24 | RESET_L        | I   | TTL        | Reset Input:  When this active-low signal is asserted, the XRT94L31 will be asynchronously reset. When this occurs, all outputs will be tri-stated and all onchip registers will be reset to their default values.                                                                                                                                                                                                                                                                                        |

| AE18 | DIRECT_ADD_SEL | I   | TTL        | Address Location Select input pin: This input pin must be pulled "High" in order to permit normal operation of the Microprocessor Interface.                                                                                                                                                                                                                                                                                                                                                              |

|      |                | 5   | SONET/S    | DH SERIAL LINE INTERFACE PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

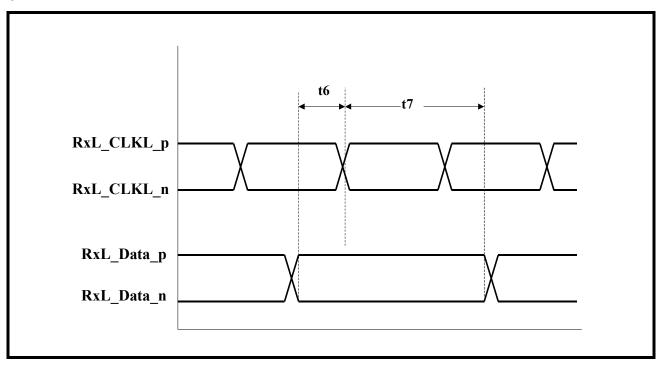

| ТЗ   | RXLDAT_P       | I   | LVPEC<br>L | Receive STS-3/STM-1 Data - Positive Polarity PECL Input:  This input pin, along with RXLDAT_N functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane  Note: For APS (Automatic Protection Switching) purposes, this input pin, along with RXLDAT_N functions as the Primary STS-3/STM-1 Receive Data Input Port.                                                                                                                     |

| T2   | RXLDAT_N       | I   | LVPEC<br>L | Receive STS-3/STM-1 Data - Negative Polarity PECL Input:  This input pin, along with RXLDAT_P functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane.  Note: For APS (Automatic Protection Switching) purposes, this input pin, along with RXLDAT_P functions as the Primary Receive STS-3/STM-1 Data Input Port                                                                                                                     |

# Experience Our Connectivity. REV. 1.0.1

| PIN# | SIGNAL NAME | I/O | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U2   | RXLDAT_R_P  | I   | LVPEC<br>L | Receive STS-3/STM-1 Data - Positive Polarity PECL Input - Redundant Port:  This input pin, along with RXLDAT_R_N functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane.  Note: For APS (Automatic Protection Switching) purposes, this input                                                                                                                                                                                                                                                                                                                            |

|      |             |     |            | pin, along with RXLDAT_R_N functions as the Redundant Receive STS-3/STM-1 Data Input Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U1   | RXLDAT_R_N  | I   | LVPEC<br>L | Receive STS-3/STM-1 Data - Negative Polarity PECL Input - Redundant Port:  This input pin, along with RXLDAT_R_P functions as the Recovered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |             |     |            | Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |             |     |            | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this input pin, along with RXLDAT_R_N functions as the Redundant Receive STS-3/STM-1 Data Input Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AE27 | RXCLK_19MHZ | 0   | CMOS       | 19.44MHz Recovered Output Clock:  This pin outputs a 19.44MHz clock signal that has been derived from the incoming STS-3/STM-1 LVPECL line signal (via the Receive STS-3/STM-1 PECL Interface block) and has been extracted out and derived by Clock and Data Recovery PLL (within the Receive STS-3/STM-1 PECL Interface block).  To operate the STS-3/STM-1 Interface of the XRT94L31 in the loop-tim-                                                                                                                                                                                                                                      |

|      |             |     |            | ing mode, route this particular output signal through a narrow-band PLL (in order to attenuate any jitter within this signal) prior to routing it to the REFTTL input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3   | REFCLK_P    | I   | LVPEC<br>L | Transmit Reference Clock - Positive Polarity PECL Input: This input pin, along with REFCLK_N and REFTTL can be configured to function as the timing source for the STS-3/STM-1 Transmit Interface Block.  If these two input pins are configured to function as the timing source, a 155.52MHz clock signal must be applied to these input pins in the form of a PECL signal. Configure these two inputs to function as the timing source by writing the appropriate data into the Transmit Line Interface Control Register (Address Location = 0x0383)  Note: If REFTTL clock input is used, set this pin to a logic "High"                  |

| P2   | REFCLK_N    | I   | LVPEC<br>L | Transmit Reference Clock - Negative Polarity PECL Input:  This input pin, along with REFCLK_P and REFTTL can be configured to function as the timing source for the STS-3/STM-1 Transmit Interface Block.  If these two input pins are configured to function as the timing source, then the user must apply a 155.52MHz clock signal, in the form of a PECL signal to these input pins. These two inputscan be configured to function as the timing source by writing the appropriate data into the Transmit Line Interface Control Register (Address Location = 0x0383).  Note: Set this pin to a logic "Low" if REFTTL clock input is used |

| PIN# | SIGNAL NAME | I/O | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-------------|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5   | TXLDATO_P   | 0   | LVPEC<br>L | Transmit STS-3/STM-1 Data - Positive Polarity LVPECL Output: This output pin, along with TXLDATO_N functions as the Transmit Data Output (from the Transmit STS-3/STM-1 PECL Interface block), to the Optical Transceiver (for transmission to remote terminal equipment) or to the system back-plane (for transmission to some other System-Board). For High-Speed Back-Plane Applications, data is output from these output pins upon the rising/falling edge of TXLCLKO_P/TXLCLKO_N.  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLDATO_N functions as the Primary Transmit STS-3/STM-1 Data Output Port.                                    |

| P6   | TXLDATO_N   | 0   | LVPEC<br>L | Transmit STS-3/STM-1 Data - Negative Polarity LVPECL Output:  This output pin, along with TXLDATO_P functions as the Transmit Data Output (from the Transmit STS-3/STM-1 PECL Interface block), to the Optical Transceiver (for transmission to remote terminal equipment) or to the system back-plane (for transmission to some other System board). For High-Speed Back-Plane Applications, data is output from these output pins upon the rising/falling edge of TXLCLKO_P/TXLCLKO_N.  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLDATO_P functions as the Primary Transmit STS-3/STM-1 Data Output Port.                                   |

| M4   | TXLDATO_R_P | 0   | LVPEC      | Transmit STS-3/STM-1 Data - Positive Polarity LVPECL Output - Redundant Port:  This output pin, along with TXLDATO_R_N functions as the Transmit Data Output (from the Transmit STS-3/STM-1 PECL Interface block), to the Optical Transceiver or to the system back-plane.  For High-Speed Back-Plane Applications, data is output from these output pins upon the rising/falling edge of TXLCLKO_R_P/TXLCLKO_R_N).  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLDATO_N functions as the Redundant Transmit STS-3/STM-4 Data Output Port.                                                                                                      |

| M3   | TXLDATO_R_N | 0   | LVPEC      | Transmit STS-3/STM-1 Data - Negative Polarity LVPECL Output - Redundant Port:  This output pin, along with TXLDATO_R_P functions as the Transmit Data Output (from the Transmit STS-3/STM-1 PECL Interface block), to the Optical Transceiver (for transmission to remote terminal equipment) or to the system back-plane (for transmission to some other System board).  For High-Speed Back-Plane Applications, data is output from these output pins upon the rising/falling edge of TXLCLKO_R_P/TXLCLKO_R_N).Note:  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLDATO_R_P functions as the Redundant Transmit STS-3/STM-1 Data Output Port. |

| PIN# | SIGNAL NAME | I/O | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N6   | TXLCLKO_P   | 0   | LVPEC<br>L | Transmit STS-3/STM-1 Clock - Positive Polarity PECL Output: This output pin, along with TXLCLKO_N functions as the Transmit Clock Output signal. These output pins are typically used in High-Speed Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the TXLDATO_P/TXLDATO_N output pins upon the rising edge of this clock signal.  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLCLKO_N functions as the Primary Transmit Output Clock signal.                              |

| N5   | TXLCLKO_N   | 0   | LVPEC<br>L | Transmit STS-3/STM-1 Clock - Negative Polarity PECL Output:  This output pin, along with TXLCLKO_P functions as the Transmit Clock Output signal.  These output pins are typically used in High-Speed Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the TXLDATO_P/TXLDATO_N output pins upon the falling edge of this clock signal.  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLCLKO_N functions as the Primary Transmit Output Clock signal.                           |

| M1   | TXLCLKO_R_P | 0   | LVPEC<br>L | Transmit STS-3/STM-1 Clock - Positive Polarity PECL Output - Redundant Port:  This output pin, along with TXLCLKO_R_N functions as the Transmit Clock Output signal.  These output pins are typically used in High-Speed Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the TXLDATO_R_P/TXLDATO_R_N output pins upon the rising edge of this clock signal.  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLCLKO_R_N functions as the Redundant Transmit Output Clock signal. |

| M2   | TXLCLKO_R_N | 0   | LVPEC<br>L | Transmit STS-3/STM-1 Clock - Negative Polarity PECL Output - Redundant Port:  This output pin, along with TXLCLKO_R_P functions as the Transmit Clock Output signal. These output pins are typically used in High-Speed Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the TXLDATO_R_P/TXLDATO_R_N output pins upon the rising edge of this clock signal.  Note: For APS (Automatic Protection Switching) purposes, this output pin, along with TXLCLKO_R_P functions as the Redundant Transmit Output Clock signal.  |

| PIN# | SIGNAL NAME | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1   | REFTTL      | I   | TTL  | 19.44MHz or 77.76MHz Clock Synthesizer Reference Clock Input Pin:                                                                                                                                                                                                                                                                                                                                       |

|      |             |     |      | The function of this input pin depends upon whether or not the Clock Synthesizer block is enabled.                                                                                                                                                                                                                                                                                                      |

|      |             |     |      | If Clock Synthesizer is Enabled.                                                                                                                                                                                                                                                                                                                                                                        |

|      |             |     |      | If the Clock Synthesizer block is enabled, then it will be used to generate the 155.52MHz, 19.44MHz and/or 77.76MHz clock signal for the Transmit STS-3/STM-1 circuitry. In this mode, the user should apply a clock signal of any of the following frequencies to this input pin.                                                                                                                      |

|      |             |     |      | • 19.44 MHz                                                                                                                                                                                                                                                                                                                                                                                             |

|      |             |     |      | • 38.88 MHz                                                                                                                                                                                                                                                                                                                                                                                             |

|      |             |     |      | • 51.84 MHz                                                                                                                                                                                                                                                                                                                                                                                             |

|      |             |     |      | • 77.76 MHz                                                                                                                                                                                                                                                                                                                                                                                             |

|      |             |     |      | Afterwards, the user needs to write the appropriate data into the Transmit Line Interface Control Register (Address Location = 0x0383) in order to (1) configure the Clock Synthesizer Block to accept any of the abovementioned signals and generate a 155.52MHz, 19.44MHz or 77.76MHz clock signal, (2) to configure the Clock Synthesizer to function as the Clock Source for the STS-3/STM-1 block. |

|      |             |     |      | If Clock Synthesizer is NOT Enabled:                                                                                                                                                                                                                                                                                                                                                                    |

|      |             |     |      | If the Clock Synthesizer block is NOT enabled, then it will NOT be used to generate the 19.44MHz and/or 77.76MHz clock signal, for the STS-3/STM-1 block. In this configuration seting, the user MUST apply a 19.44MHz clock signal to this input pin.                                                                                                                                                  |

|      |             |     |      | <b>NOTE:</b> The user must place a clock signal to this input pin in order to perform READ and WRITE operations to much of the SONET/SDH-related registers via the Microprocessor Interface.                                                                                                                                                                                                            |

| PIN# | SIGNAL NAME | I/O | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DESCRIPTION                 |                                      |                                                                                                                  |  |  |  |  |

|------|-------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AG3  | LOSTTL      | ı   | TTL  | Loss of Optical Carrier Input - Primary Receive STS-3/STM-1 PECL Interface - TTL Input:  If the user is using an Optical Transceiver that contains an LOS (or Signal Detect) output that is of the CMOS/TTL format, then connect this LOS output signal to this input pin of the XRT94L31.  Configure the LOSTTL input pin to be either an active-low or an active-high signal, by pulling the LOSPECL input pin to the appropriate level as described below. |                             |                                      |                                                                                                                  |  |  |  |  |

|      |             |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LOSPECL                     | LOSTTL<br>Active-Low/<br>Active-High | Description of LOSTTL                                                                                            |  |  |  |  |

|      |             |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GND                         | Active-Low                           | Setting this input pin "low" configures the Receive Line Interface block to declare the "LOS_Detect" condition.  |  |  |  |  |

|      |             |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VDD                         | Active-High                          | Setting this input pin "high" configures the Receive Line Interface block to declare the "LOS_Detect" condition. |  |  |  |  |

|      |             |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             | ulled to the appr                    | opriate state such that LOS is TRUE, happen.                                                                     |  |  |  |  |

|      |             |     |      | l .                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                           | ceive STS-3 To                       | OH Processor block will declare the .                                                                            |  |  |  |  |

|      |             |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e Primary Red<br>LOS_Detect |                                      | M-1 Line Interface block will declare                                                                            |  |  |  |  |

|      |             |     |      | NOTE                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRUE, this                  | (by itself) will N                   | the appropriate state such that LOS is OT cause the Primary Receive STS-3 eclare the LOS defect condition.       |  |  |  |  |

| PIN# | SIGNAL NAME | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |  |  |  |  |  |

|------|-------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|

| AG25 | LOSTTL_R    | I   | TTL  | Loss of Optical Carrier Input - Redundant Receive STS-3/STM-1 PECL Interface - TTL Input:  If the user is using the Optical Transceiver that contains an LOS (or Signal Detect) output that is of the CMOS/TTL format, then connect this LOS output signal to this input pin of the XRT94L31.  Configure the LOSTTL_R input pin to either an active-low or an active-high signal, by pulling the LOSPECL_R input pin to the appropriate level as described below.                                                        |                            |  |  |  |  |  |

|      |             |     |      | LOSTTL_R LOSPECL_R Active-Low/ Active-High                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |  |  |  |  |  |

|      |             |     |      | GND  Active-Low  Setting this input pin "low" configures the Redundant Receive Line Interface block to declare the "LOS_Detect" condition.                                                                                                                                                                                                                                                                                                                                                                               |                            |  |  |  |  |  |

|      |             |     |      | VDD Active-High Setting this input pin "high" configures the Redundant Receive Line Interface block to declare the "LOS_Detect" condition.                                                                                                                                                                                                                                                                                                                                                                               |                            |  |  |  |  |  |

|      |             |     |      | If this input pin is pulled to the appropriate state such that LOS is TR then all of the following events will happen.  The Redundant Receive STS-3 TOH Processor block wil declare the Loss of Optical Carrier condition  The Redundant Receive STS-3/STM-1 Line Interface block will declare the LOS_Detect condition.  Note: If this input pin is pulled to the appropriate state such that LOS_TRUE, this (by itself) will NOT cause the Redundant Receive STS-3 TOH Processor block to declare the LOS decondition. | e<br>are<br>OS is<br>ceive |  |  |  |  |  |

| PIN# | SIGNAL NAME | I/O | TYPE       |                                |                                                                                          | DESCR                                                                                                                     | RIPTION                                                                                                                                                                                                            |

|------|-------------|-----|------------|--------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L4   | LOSPECL_P   | I   | LVPEC<br>L | Input If the nat I LOS Control | ut - Primary Receive user is using a Detect) output pit output signal to figure the LOSP | ceive STS-3/ST<br>in Optical Transo<br>in that is of the L<br>o this input pin o<br>PECL_P input pir<br>by pulling the LC | ut - Single-Ended PECL Interface M-1 PECL Interface: ceiver that contains an LOS (or Sig-VPECL format, then connect this f the XRT94L31. In to function as either an active-low DSTTL input pin to the appropriate |

|      |             |     |            |                                | LOSTTL                                                                                   | LOSPECL_P<br>Active-Low/<br>Active-High                                                                                   | Description of LOSPECL_P                                                                                                                                                                                           |

|      |             |     |            |                                | GND                                                                                      | Active-Low                                                                                                                | Setting this input pin "low" configures the Receive Line Interface block to declare the "LOS_Detect" condition.                                                                                                    |

|      |             |     |            |                                | VDD                                                                                      | Active-High                                                                                                               | Setting this input pin "high" configures the Receive Line Interface block to declare the "LOS_Detect" condition.                                                                                                   |

|      |             |     |            | then                           | all of the follow                                                                        | ing events will h                                                                                                         | • •                                                                                                                                                                                                                |

|      |             |     |            |                                | ne Primary Rec<br>oss of Optical Ca                                                      |                                                                                                                           | H Processor block will declare the                                                                                                                                                                                 |

|      |             |     |            |                                | ne Primary Rec<br>e LOS_Detect c                                                         |                                                                                                                           | /I-1 Line Interface block will declare                                                                                                                                                                             |

|      |             |     |            | Not                            | TRUE, this (                                                                             | (by itself) will NC                                                                                                       | ne appropriate state such that LOS is DT cause the Primary Receive STS-3 clare the LOS defect condition.                                                                                                           |

| PIN# | SIGNAL NAME | I/O | TYPE       |                                  |                                                                                        | DESCR                                                                                                | RIPTION                                                                                                                                                                                                                          |