#### Is Now Part of

## ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

September 2014

## FTL11639 Configurable Load Switch and Reset Timer

#### **Features**

- Factory Customized Turn-on Time: 38 ms

- Factory Customized Turn-off Delay: 900 ms

- Factory Programmed Reset Delay: 11.5 s

- Factory Programmed Reset Pulse: 400 ms

- Adjustable Reset Delay Option with External Resistor

- Low < 0.2 µA Typical Shutdown Current

- Off Pin Turns Off Load Switch to Maintain Battery Charge during Shipment and Inventory (Ready to Use Right Out of the Box)

- Typical R<sub>ON</sub>: 21 m $\Omega$  (Typ.) at V<sub>BAT</sub>=4.5 V

- 3.8 A / 4.5 A Maximum Continuous Current (JEDEC 2S2P, No VIA / with Thermal VIA)

- Low I<sub>CCT</sub> Saves Power Interfacing to Low-Voltage Chips

- Input Voltage Operating Range: 1.2 V to 5.5 V

- Over-Voltage Protection: Allow Input Pins > VBAT

- Slew Rate / Inrush Control with t<sub>R</sub>: 2.7 ms (Typical)

- **Output Capacitor Discharge Function**

- Zero-Second Test-Mode Enable

- IEC61000-4-2, Level 4 compliant SYS\_WAKE Pin

- **ESD Protected:**

- 8 kV HBM ESD (per JESD22-A114)

- 10 kV HBM ESD (Pin to Pin, V<sub>BAT</sub> & V<sub>OUT</sub>)

- 2 kV CDM (per JESD22-C101)

## **Applications**

- Smart Phones, Tablet PCs

- Storage, DSLR, and Portable Devices

## **Description**

The FTL11639 is both a timer for resetting a mobile device and an advanced load management device for applications requiring a highly integrated solution.

If the mobile device is off, holding /SR0 LOW (by pressing power-on key) for 38 ms ±20% turns on the PMIC.

As a reset timer, it has one input and one fixed delay output. It generates a fixed delay of 11.5 s ±20% by disconnecting the PMIC from the battery power supply. FTL11639 does not accept a new input signal for 400 ms ±20% to give the PMIC enough time to turn off.

The reset delay can be customized by connecting an external resistor to the DELAY\_ADJ pin. Refer to Table 5.

As an advanced load management switch, the FTL11639 disconnects loads powered from the DC power rail (<6 V) with stringent off-state current targets and high load capacitances (up to 200 µF). The FTL11639 consists of a slew-rate controlled low-impedance MOSFET switch (21 mΩ typical at 4.5 V) that has exceptionally low off-state current drain (<0.2 µA typical) to facilitate compliance with standby power requirements. The slew-rate-controlled turn-on characteristic prevents inrush current and the resulting excessive voltage drop on power rails.

The low I<sub>CCT</sub> enables direct interface to lower-voltage chipsets without external translation, while maintaining low power consumption.

The device is packaged in advanced, fully "green," 1.31 mm x 1.62 mm, Wafer-Level Chip-Scale Packaging (WLCSP) with backside laminate; providing excellent thermal conductivity, small footprint, and low electrical resistance for a wide application range.

#### Related Resources

For additional information, please contact: http://www.fairchildsemi.com/cf/#Regional-Sales

## **Ordering Information**

| Part Number | Top<br>Mark | Operating<br>Temperature Range | Package                                                                                                        | Packing Method                 |

|-------------|-------------|--------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------|

| FTL11639UCX | UC          | -40 to +85°C                   | 12-Ball WLCSP (with backside laminate),<br>3x4 Array, 0.4 mm Pitch, 250 µm Ball,<br>Nominal: 1.31 mm x 1.62 mm | 3000 Units on<br>Tape and Reel |

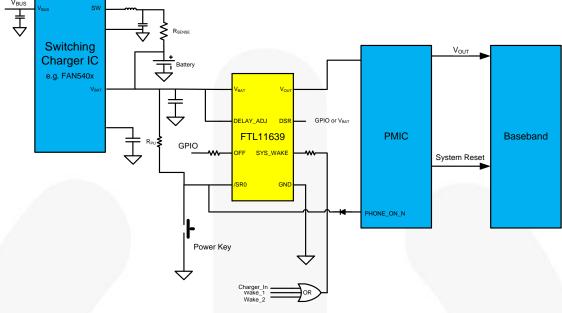

## **Application Diagram**

Figure 1. Typical Application with Stand Alone Switching Charger IC

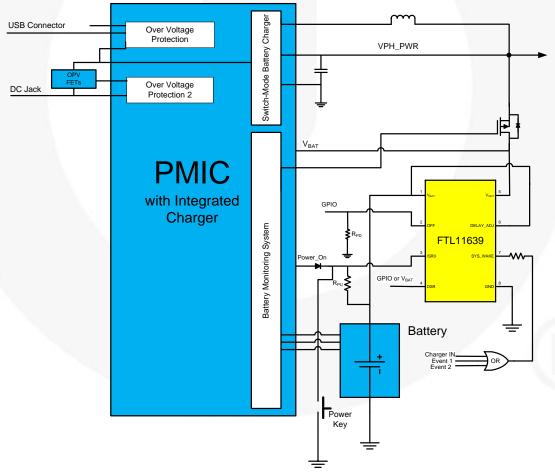

Figure 2. Typical Application PMIC with Integrated Charger

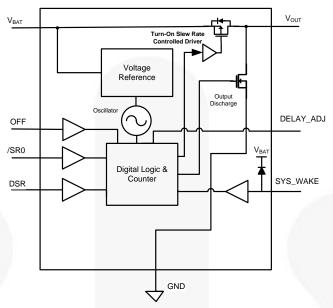

## **Functional Block Diagram**

Figure 3. Block Diagram

## **Pin Configuration**

Figure 4. Top View

Figure 5. Bottom View

## **Pin Definitions**

| Pin#       | Name             | Description                                                                                                                                                       |                                           |  |  |  |

|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| PIII #     | Name             | Normal Operation                                                                                                                                                  | 0-Second Factory-Test Mode <sup>(1)</sup> |  |  |  |

| A1, A2, A3 | V <sub>OUT</sub> | Switch Output                                                                                                                                                     | Switch Output                             |  |  |  |

| B1, B2, B3 | $V_{BAT}$        | Supply Input                                                                                                                                                      | Supply Input                              |  |  |  |

| C1         | GND              | Ground                                                                                                                                                            | Ground                                    |  |  |  |

| C2         | DSR              | Delay selection input; connected to GPIO with a 100 k $\Omega$ pull-up resistor or to $V_{BAT}$ directly without pull-up resistor                                 | Logic LOW                                 |  |  |  |

| C3         | /SR0             | Power-on or reset input; active LOW                                                                                                                               | Logic LOW                                 |  |  |  |

| D1         | DELAY_ADJ        | Reset delay adjustment; MUST tie to $V_{BAT}$ directly if not used. To adjust the reset delay, a resistor ( $R_{ADJ}$ ) is connected between this pin and ground. | Connected to V <sub>BAT</sub> or GND      |  |  |  |

| D2         | OFF              | Load switch disable; falling edge triggered; changes load switch from ON state to OFF state                                                                       | Don't Care                                |  |  |  |

| D3         | SYS_WAKE         | System wake-up input; changes load switch from OFF state to ON state                                                                                              | Don't Care                                |  |  |  |

#### Note:

1. Zero-Second Factory Test Mode is for  $t_{VON}$  and  $t_{PHL1}$  only.

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameters                                          |                                     | Condition                                       | Min. | Max.                  | Unit |

|-------------------|-----------------------------------------------------|-------------------------------------|-------------------------------------------------|------|-----------------------|------|

| $V_{BAT}$         | V <sub>BAT</sub> to GND                             |                                     |                                                 | 0.0  | 0.5                   | V    |

| V <sub>OUT</sub>  | V <sub>OUT</sub> to GND                             |                                     |                                                 | -0.3 | 6.5                   | V    |

| Laur              | Maximum Continuous Switch Current                   | 2S2P JEI                            | DEC std. PCB                                    |      | 3.8                   | Α    |

| I <sub>SW</sub>   | Maximum Continuous Switch Current                   | 2S2P + T                            | hermal VIA JEDEC std. PCB                       |      | 4.7                   | А    |

| $P_D$             | Power Dissipation                                   | I <sub>OUT</sub> =4.5               | A, $R_{ON} = 20 \text{ m}\Omega \text{ (Max.)}$ |      | 0.41                  | W    |

| $V_{IN}$          | DC Input Voltage                                    | /SR0, DS                            | R, OFF, DELAY_ADJ                               | -0.5 | 6.5                   | V    |

| VIN               | DC Input Voltage                                    | SYS_WA                              | KE <sup>(2)</sup>                               |      | V <sub>BAT</sub> +0.3 | V    |

| $I_{IK}$          | DC Input Diode Current                              | $V_{BAT} < 0$                       | V                                               |      | -50                   | mΑ   |

| Icc               | DC V <sub>CC</sub> or Ground Current per Supply Pin |                                     |                                                 |      | ±100                  | mΑ   |

| T <sub>STG</sub>  | Storage Temperature Range                           |                                     |                                                 |      | +150                  | °C   |

| TJ                | Junction Temperature Under Bias                     |                                     |                                                 |      | +150                  | °C   |

| TL                | Junction Lead Temperature, Soldering 1              | 0 Seconds                           |                                                 |      | +260                  | °C   |

|                   | Thermal Resistance, Junction-to-Ambient             |                                     | 2S2P JEDEC std. PCB                             |      | 86                    |      |

| $\Theta_{\sf JA}$ |                                                     |                                     | 2S2P + Thermal VIA<br>JEDEC std. PCB            |      | 48                    | °C/W |

| $\Theta_{\sf JC}$ | Thermal Resistance, Junction-to-Case <sup>(3)</sup> | )                                   |                                                 | 1    | 10.9                  | °C/W |

|                   | Human Body Model, JEDEC: JESD22-A                   | All Pins                            |                                                 | 8    |                       |      |

|                   | Human Body Model, Pin to Pin <sup>(4)</sup>         | V <sub>BAT</sub> , V <sub>OUT</sub> |                                                 | 10   | kV                    |      |

| ESD               | JEO 04000 0 4 J 2001 4 for OVO MAKE <sup>(5)</sup>  |                                     | Air                                             |      |                       | 15   |

|                   | IEC 61000-2-4, Level 4, for SYS_WAKE                | 4, for SYS_WAKE Contact             |                                                 |      | 8                     |      |

|                   | Charged Device Model, JESD22-C101                   |                                     | 2                                               |      |                       |      |

#### Notes:

- 2. SYS\_WAKE operates up to 28 V if an external resistor is attached. A value of 100 k $\Omega$  is typically recommended.

- 3. Uniform temperature at bottom solder.

- Test conditions: V<sub>BAT</sub> vs. GND and V<sub>OUT</sub> vs. GND.

- 5. A 100 k $\Omega$  resistor is required.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol           | Parameters                                      | Condition                                               | Min. | Max.                      | Unit |

|------------------|-------------------------------------------------|---------------------------------------------------------|------|---------------------------|------|

| V <sub>BAT</sub> |                                                 | V <sub>BAT</sub>                                        | 1.2  | - 5.5<br>V <sub>BAT</sub> |      |

| \/               | Input Voltage <sup>(6)</sup>                    | /SR0, DSR, OFF                                          | 0    |                           | V    |

| V <sub>IN</sub>  |                                                 | SYS_WAKE                                                | 0    |                           |      |

| V <sub>OUT</sub> | Output Voltage                                  |                                                         | 0    | 5.5                       | V    |

|                  | Maximum Continuous Switch Current               | 2S2P JEDEC std. PCB                                     |      | 3.8                       | ^    |

| I <sub>SW</sub>  | Maximum Continuous Switch Current               | 2S2P + Thermal VIA JEDEC std. PCB                       |      | 4.5                       | А    |

| t <sub>RFC</sub> | V <sub>BAT</sub> Recovery Time After Power Down | V <sub>BAT</sub> =0 V After Power Down, Rising to 0.5 V | 5    |                           | ms   |

| T <sub>A</sub>   | Free-Air Operating Temperature                  |                                                         | -40  | +85                       | °C   |

#### Note:

6. V<sub>BAT</sub> should never be allowed to float while input pins are driven.

## **Electrical Characteristics**

Unless otherwise noted,  $V_{BAT}$ =1.2 to 5.5 V and  $T_A$ =-40 to +85°C; typical values are at  $V_{BAT}$ =4.5 V and  $T_A$ =25°C.

| Symbol           | Parameters                              | Conditions                                                                                                             | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Basic Op         | peration                                |                                                                                                                        |      | l    |      | .1   |

| I <sub>OFF</sub> | Off Supply Current                      | V <sub>BAT</sub> =4.5 V, V <sub>OUT</sub> =Open, Load Switch=OFF                                                       |      |      | 5.5  | μA   |

|                  | Object days are Comment                 | V <sub>BAT</sub> =4.5 V, V <sub>OUT</sub> =GND, Load Switch=OFF                                                        |      | 0.2  | 5.5  |      |

| I <sub>SD</sub>  | Shutdown Current                        | V <sub>BAT</sub> =3.8 V, V <sub>OUT</sub> =GND, Load Switch=OFF                                                        |      | 0.1  | 4.5  | μA   |

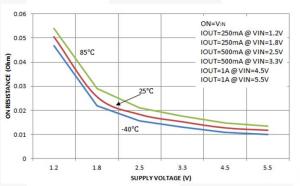

|                  |                                         | V <sub>BAT</sub> =5.5 V, I <sub>OUT</sub> =1 A <sup>(7)</sup>                                                          |      | 20   | 24   |      |

|                  |                                         | V <sub>BAT</sub> =4.5 V, I <sub>OUT</sub> =1 A, T <sub>A</sub> =25°C <sup>(7)</sup>                                    |      | 21   | 25   |      |

| R <sub>ON</sub>  | On Resistance                           | V <sub>BAT</sub> =3.3 V, I <sub>OUT</sub> =500 mA <sup>(7)</sup>                                                       |      | 24   | 29   | mΩ   |

| NON              | On Resistance                           | V <sub>BAT</sub> =2.5 V, I <sub>OUT</sub> =500 mA <sup>(7)</sup>                                                       |      | 28   | 35   |      |

|                  |                                         | V <sub>BAT</sub> =1.8 V, I <sub>OUT</sub> =250 mA <sup>(7)</sup>                                                       |      | 37   | 45   |      |

|                  |                                         | V <sub>BAT</sub> =1.2 V, I <sub>OUT</sub> =250 mA, T <sub>A</sub> =25°C <sup>(7)</sup>                                 |      | 75   | 100  |      |

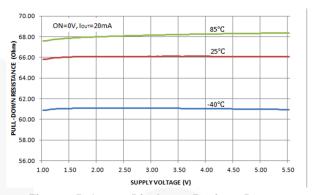

| $R_{PD}$         | Output Discharge R <sub>PULL DOWN</sub> | V <sub>BAT</sub> =4.5 V, V <sub>OUT</sub> =OFF, I <sub>FORCE</sub> =20 mA, T <sub>A</sub> =25°C                        |      | 65   | 85   | Ω    |

| \/               | Input High Voltage <sup>(8)</sup>       | 1.8 V <v<sub>BAT≤5.5 V</v<sub>                                                                                         | 1.2  |      |      | V    |

| V <sub>IH</sub>  | Input High Voltage                      | 1.2 V≤V <sub>BAT</sub> ≤1.8 V                                                                                          | 1.0  |      | 171  | V    |

| V <sub>IL</sub>  | Input Low Voltage <sup>(8)</sup>        |                                                                                                                        |      |      | 0.45 | V    |

| I <sub>IN</sub>  | Input Leakage Current <sup>(8)</sup>    | $0~V \leq V_{BAT} \leq 5.5~V$                                                                                          |      |      | ±1.5 | μΑ   |

|                  |                                         | /SR0=5.5 V, DSR=5.5 V,<br>SYS_WAKE=5.5 V, OFF =GND, I <sub>OUT</sub> =0 mA,<br>V <sub>BAT</sub> =5.5 V, Load Switch=ON |      | 5.0  | 7.0  |      |

| I <sub>CCQ</sub> | Quiescent Current                       | /SR0=3.8V, DSR=3.8 V,<br>SYS_WAKE=3.8 V, OFF=GND, I <sub>OUT</sub> =0 mA,<br>V <sub>BAT</sub> =3.8 V, Load Switch=ON   |      | 4.0  | 5.5  | μA   |

| Ісст             |                                         | /SR0=1.2 V or DSR=1.2 V or OFF=1.2 V,<br>SYS_Wake=1.2 V, V <sub>BAT</sub> =5.5 V, Load Switch<br>=ON                   |      | 7.0  | 12.0 | μA   |

| Icc              | Dynamic Supply Current                  | /SR0=GND, DSR=5.5 V, V <sub>BAT</sub> =5.5 V, Load<br>Switch=ON                                                        |      |      | 60   | μΑ   |

#### Notes:

- 7. This parameter is guaranteed by design and characterization; R<sub>ON</sub> is tested with different voltage and current condition in production.

- 8. Input pins are /SR0, OFF, DSR, and SYS\_WAKE. Input pins should not be floated when V<sub>BAT</sub> is connected to the power supply.

## **AC Electrical Characteristics**

Unless otherwise noted, V<sub>BAT</sub>=1.2 to 5.5 V and T<sub>A</sub>=-40 to +85°C; typical values are at V<sub>BAT</sub>=4.5 V and T<sub>A</sub>=25°C.

| Symbol            | Parameter                                                  | Conditions                                                                                            | Min. | Тур. | Max. | Unit |

|-------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| Power-On          | and Reset Timing                                           |                                                                                                       | •    | •    | •    |      |

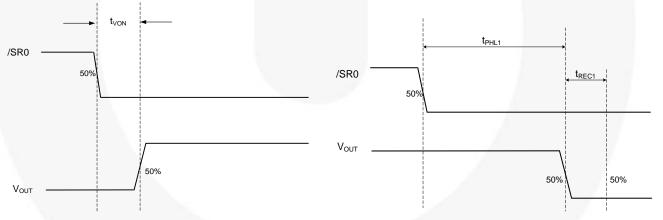

| t <sub>VON</sub>  | Turn-On Time for V <sub>OUT</sub>                          | $C_L$ =5 pF, $R_L$ =5 k $\Omega$ , DSR=HIGH, Figure 30                                                | 30   | 38   | 46   | ms   |

| t <sub>PHL1</sub> | Timer Delay before Reset                                   | $C_L$ =5 pF, $R_L$ =5 k $\Omega$ , DSR=HIGH, Figure 31                                                | 9.2  | 11.5 | 13.8 | S    |

| t <sub>REC1</sub> | Reset Timeout Delay of V <sub>OUT</sub>                    | $C_L=5$ pF, $R_L=5$ k $\Omega$ , Figure 31                                                            | 320  | 400  | 480  | ms   |

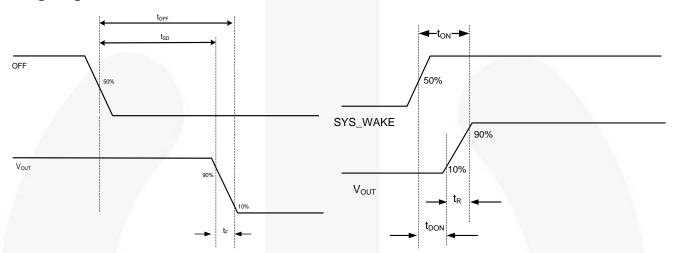

| Load Swit         | tch Turn-On Timing                                         |                                                                                                       |      |      | •    |      |

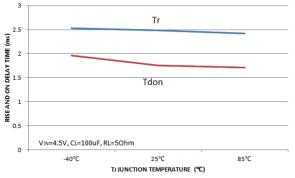

| t <sub>DON</sub>  | Turn-On Delay <sup>(9)</sup>                               | .//                                                                                                   |      | 1.7  |      | ms   |

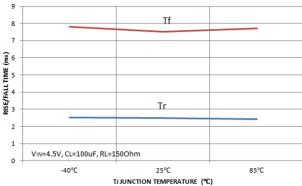

| t <sub>R</sub>    | V <sub>OUT</sub> Rise Time <sup>(9)</sup>                  | $V_{BAT}$ =4.5 V, R <sub>L</sub> =5 Ω, C <sub>L</sub> =100 μF,<br>$T_{A}$ =25°C, Figure 29            |      | 2.7  |      | ms   |

| t <sub>ON</sub>   | Turn-On Time <sup>(9)</sup> , SYS_WAKE to V <sub>OUT</sub> | -   1 <sub>A</sub> -23 0, 1 iguie 23                                                                  |      | 4.4  |      | ms   |

| Load Swit         | tch Turn-Off with Delay                                    |                                                                                                       | •    |      |      |      |

| t <sub>SD</sub>   | Delay to Turn Off Load Switch                              |                                                                                                       | 720  | 900  | 1080 | ms   |

| t <sub>F</sub>    | V <sub>OUT</sub> Fall Time <sup>(9)</sup>                  | $V_{BAT}$ =4.5 V, R <sub>L</sub> =150 Ω, C <sub>L</sub> =100 μF, $V_{A}$ =25°C, DSR=HIGH, Figure 28   |      | 10   |      | ms   |

| t <sub>OFF</sub>  | Turn-Off <sup>(10,11)</sup>                                | TA-23 C, DON-HIGH, Figure 20                                                                          |      | 910  |      | ms   |

| Load Swit         | tch Zero-Second Turn-Off                                   |                                                                                                       |      |      |      |      |

| t <sub>SD</sub>   | Delay to Turn Off Load Switch                              |                                                                                                       |      | 0.6  |      | ms   |

| t <sub>F</sub>    | V <sub>OUT</sub> Fall Time <sup>(9)</sup>                  | $V_{BAT}$ =4.5 V, R <sub>L</sub> =150 Ω, C <sub>L</sub> =100 μF,<br>$T_{A}$ =25°C, DSR=LOW, Figure 28 |      | 10.0 |      | ms   |

| t <sub>OFF</sub>  | Turn-Off <sup>(10,11)</sup>                                | 1,4-20 0, DON-LOW, 1 iguie 20                                                                         |      | 10.6 |      | ms   |

#### Notes:

- 9.  $t_{ON}=t_R + t_{DON}$ .

- 10.  $t_{OFF}=t_F + t_{SD}$ .

- 11. Output discharge enabled during off-state.

## **Zero-Second Factory Test Mode**

Unless otherwise noted,  $V_{BAT}$ =1.2 to 5.5 V and  $T_A$ =-40 to +85°C; typical values are at  $V_{BAT}$ =4.5 V and  $T_A$ =25°C.

| Symbol            | Parameter                         | Conditions                                                            | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------|-----------------------------------------------------------------------|------|------|------|------|

| t <sub>VON</sub>  | Turn-On Time for V <sub>OUT</sub> | $C_L$ =5 pF, $R_L$ =5 k $\Omega$ , $V_{OUT}$ =OFF, DSR=LOW, Figure 30 |      | 4    |      | ms   |

| t <sub>PHL1</sub> | Timer Delay before Reset          | $C_L$ =5 pF, $R_L$ =5 k $\Omega$ , $V_{OUT}$ =ON, DSR=LOW, Figure 31  |      | 1    |      | ms   |

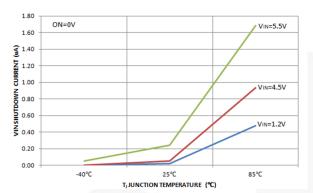

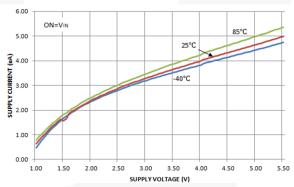

## **Typical Characteristics**

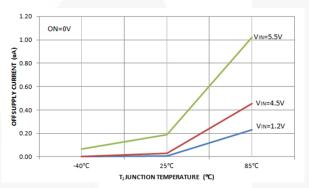

Figure 6. Shutdown Current vs. Temperature

Figure 8. Off Supply Current vs. Temperature (V<sub>OUT</sub>=0 V)

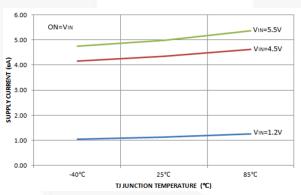

Figure 10. Quiescent Current vs. Temperature

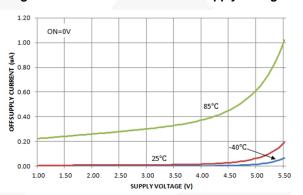

Figure 7. Shutdown Current vs. Supply Voltage

Figure 9. Off Supply Current vs. Supply Voltage (V<sub>Ουτ</sub>=0 V)

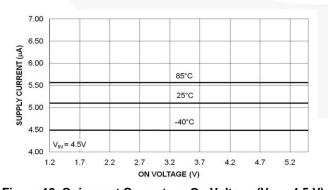

Figure 11. Quiescent Current vs. Supply Voltage

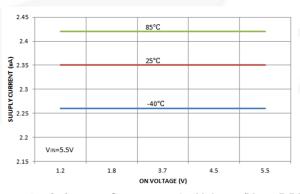

Figure 12. Quiescent Current vs. On Voltage (VBAT=4.5 V) Figure 13. Quiescent Current vs. On Voltage (VBAT=5.5 V)

## **Typical Characteristics**

0.06

0.05

0.04

0.03

0.01

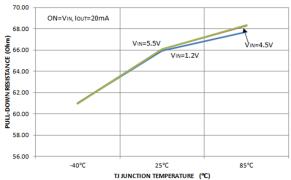

Figure 14. Output Discharge Resistor R<sub>PD</sub> vs. Temperature

VIN=1.2V

Figure 16. Ron vs. Temperature

VIN=4.5V

VIN=5.5V

TIJUNCTION TEMPERATURE (°C)

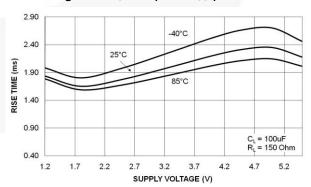

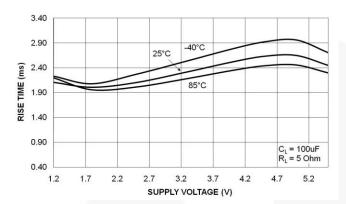

Figure 18. t<sub>R</sub>/t<sub>F</sub> vs. Temperature

Figure 20. t<sub>R</sub>/t<sub>DON</sub> vs. Temperature

Figure 15. Output Discharge Resistor R<sub>PD</sub> vs. Supply Voltage

Figure 17. Ron vs. Supply Voltage

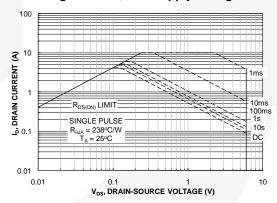

Figure 19. I<sub>SW</sub> vs. (V<sub>IBAT</sub>-V<sub>OUT</sub>) — SOA

Figure 21. t<sub>R</sub> vs. Supply Voltage

## **Typical Characteristics**

Figure 22. t<sub>R</sub> vs. Supply Voltage

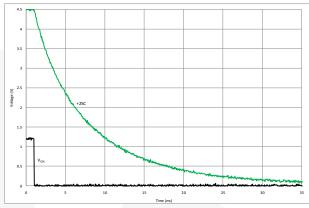

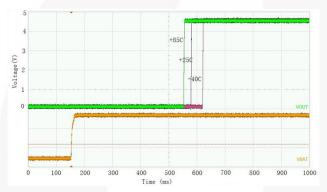

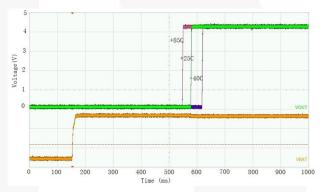

Figure 23. Turn-Off Response ( $V_{BAT}$ =4.5 V,  $C_{IN}$ =10  $\mu$ F,  $C_L$ =100  $\mu$ F, without External  $R_L$ )

Figure 24. Turn-On Response (V<sub>BAT</sub>=4.5 V, C<sub>IN</sub>=10  $\mu$ F, C<sub>L</sub>=1  $\mu$ F, R<sub>L</sub>=50  $\Omega$ )

Figure 25. Turn-On Response (V<sub>BAT</sub>=4.5 V, C<sub>IN</sub>=10  $\mu$ F, C<sub>L</sub>=100  $\mu$ F, R<sub>L</sub>=5  $\Omega$ )

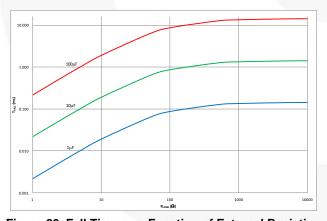

Figure 26. Fall Time as a Function of External Resistive Load (CL=1  $\mu F$ , 10  $\mu F$ , and 100  $\mu F$ )

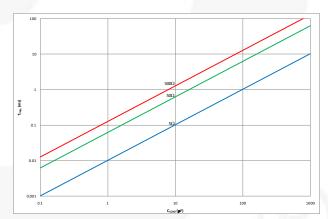

Figure 27. Fall Time as a Function of External Capacitive Load (R<sub>L</sub>=5  $\Omega$ , 50  $\Omega$ , and 500  $\Omega$ )

## **Application Information**

## **Reset Timer and Advanced Load Management**

The FTL11639 is both a reset IC and an advanced load management device. A typical application is shown in Figure 1.

#### Disconnect PMIC from Battery with OFF Pin (Turn Off)

After holding the DSR pin HIGH, the OFF pin changes from HIGH to LOW (falling edge triggered) and remains LOW for at least 1 ms. The FTL11639 triggers an internal counter to allow a factory-customized 900 ms delay before turning off internal load switch. The delay allows the PMIC to complete a power-down sequence before safely disconnecting from the power supply. However, the turn-off sequence is terminated if a higher priority input is detected in t<sub>SD</sub> period (see Resolving Input Conflicts).

Alternatively, after holding DSR pin LOW, the OFF pin changes from HIGH to LOW (falling edge triggered) and remains LOW for at least 1 ms. The FTL11639 triggers the zero-second turn-off. Delay  $t_{\rm SD}$  is significantly reduced to 0.6 ms to avoid the default delay to turn-off load switch ( $t_{\rm SD}$ ).

With its stringent shutdown current flow, the FTL11639 significantly reduces the current drain on a battery when the PMIC is turned off, preserving battery power for a longer period when a mobile device is in Shutdown Mode.

#### Power On

There are two methods to turn on the load switch to wake up the PMIC. When a HIGH is inserted to the SYS\_WAKE pin or when /SR0 is held LOW for > 38 ms (see Figure 30); FTL11639 turns on its load switch to allow the PMIC to connect to the battery. The reset feature is disabled when  $V_{OUT}$  is toggled from OFF to ON. Continuously holding /SR0 LOW does not trigger a reset event.

To enable the reset feature, /SR0 must return to HIGH such that FTL11639 resets its internal counter.

#### Reset Timer and Power Off with /SR0 Pin

During normal operation of a mobile device, if a reset operation or a power-off event is needed; holding the power switch, to which /SR0 is connected and is forced LOW, for at least 11.5 s causes the FTL11639 to cut off the supply power to PMIC. FTL11639 does not accept any new input signal for 400 ms  $\pm 20\%$  to give the PMIC enough time to turn off.

After reset, the load switch remains in OFF state and the /SR0 must return to HIGH before any new input signal is accepted. However, when load switch is in ON state and /SR0 is forced to LOW, in event of /SR0 returning to HIGH within 11.5 s, the FTL11639 resets its counter and  $V_{\text{OUT}}$  remains in ON state; there is no change on  $V_{\text{OUT}}$  and a reset does not occur.

#### **Power-On Reset**

When the FTL11639 is connected to a battery ( $V_{BAT} \ge 1.2 \text{ V}$ ), the part goes into Power-On Reset (POR) Mode. All internal registers are reset and  $V_{OUT}$  is ON at the end of POR sequence (see Table 2).

#### **Zero-Second Factory Test Mode**

FTL11639 includes a Zero-Second Factory Test Mode to shorten the turn-on time for  $V_{OUT}$  ( $t_{VON}$ ) and timer delay before reset ( $t_{PHL1}$ ) for factory testing.

When  $V_{\text{OUT}}$  is OFF, the default turn-on time ( $t_{\text{VON}}$ ) is 38 ms. If the DSR pin is LOW prior to /SR0 going LOW, the FTL11639 bypasses the 38 ms delay and  $V_{\text{OUT}}$  is changed from OFF to ON immediately.

Similarly, default reset delay ( $t_{PHL1}$ ) is 11.5 s. If  $V_{OUT}$  is ON and the DSR pin is LOW prior to /SR0 going LOW, the FTL11639 enters Zero-Second Factory Test Mode and bypasses the default reset delay of 11.5 s;  $V_{OUT}$  is pulled from ON to OFF immediately. The reset pulse ( $t_{REC1}$ ) remains at 400 ms in Zero-Second Factory Test Mode.

The DSR pin should never be left floating during normal operation.

Table 1. V<sub>OUT</sub> and Input Conditions

| Function       |      | Initial Conditions (t=0 Second) |      |      | Associated Delay                                                       | V <sub>OUT</sub> |       |

|----------------|------|---------------------------------|------|------|------------------------------------------------------------------------|------------------|-------|

| Function       | /SR0 | SYS_WAKE                        | OFF  | DSR  | (Typical)                                                              | Before           | After |

| 1/2            | LOW  | X <sup>(12)</sup>               | Х    | LOW  | t <sub>VON</sub> < 4 ms                                                | OFF              | ON    |

| Power-On       | LOW  | X                               | X    | HIGH | t <sub>VON</sub> =38 ms                                                | OFF              | ON    |

|                | HIGH | HIGH                            | Х    | Х    | t <sub>ON</sub> =4.4 ms                                                | OFF              | ON    |

| Reset Function | LOW  | ×                               | X    | LOW  | $t_{PHL1}$ < 1 ms $t_{REC1}$ =400 ms                                   | ON               | OFF   |

| (Power-Off)    | LOW  | Х                               | Х    | HIGH | t <sub>PHL1</sub> =11.5 s <sup>(13)</sup><br>t <sub>REC1</sub> =400 ms | ON               | OFF   |

| Turn Off       | HIGH | LOW                             | (12) | LOW  | t <sub>SD</sub> < 1 ms                                                 | ON               | OFF   |

| Tuill Oil      | HIGH | LOW                             |      | HIGH | t <sub>SD=</sub> 900 ms                                                | ON               | OFF   |

#### Notes:

- 12. X=Don't care,  $\Box$  = falling edge.

- 13. Reset delay (t<sub>PHL1</sub>) is adjustable (see Table 5).

Table 2. Pin Condition after POR

| Pin Name                  | /SR0 | DSR | SYS_WAKE | OFF | V <sub>out</sub> |

|---------------------------|------|-----|----------|-----|------------------|

| Default State (after POR) | 1    | 1   | 0        | 1   | ON               |

#### Note:

14. 1=input logic HIGH; 0=input logic LOW; ON=load switch is in ON state.

## **Timing Diagrams**

Figure 28. Timing Diagram (OFF vs. V<sub>OUT</sub>)

Figure 29. Timing Diagram (SYS\_WAKE vs. Vout)

Figure 30. Power On with /SR0

Figure 31. Reset Timing

## **Resolving Input Conflict**

FTL11639 allows multiple inputs at the same time and can resolve conflicts based on the priority level (see Table 3). When two input pins are triggered at the same time, only the higher priority input is served and the lower priority input is being ignored. To have the lower-priority signal serviced, it must be repeated.

**Table 3. Input Priority**

| Input    | Priority (1=Highest) |

|----------|----------------------|

| /SR0     | 1                    |

| SYS_WAKE | 2                    |

| OFF      | 3                    |

#### Special Note on OFF Pin

In the  $t_{SD}$  period (DSR=HIGH only, see Figure 28); if /SR0 or SYS\_WAKE is triggered when 0 < t <  $t_{SD}$ , the FTL11639 exits the turn-off sequence and  $V_{OUT}$  remains in ON state. The higher priority input is served regardless of the condition of the OFF pin.

To re-initiate the turn-off sequence, the OFF pins must return to HIGH, then toggle from HIGH to LOW again. The same input priority applies (*Table 3*) if DSR = HIGH.

#### **Application-Specific Note on OFF Pin**

It is a common to place FTL11639 between the battery and the PMIC. In this configuration, the input to the OFF pin is logic LOW after the FTL11639 completes the POR. This is because the OFF pin is commonly tied to the I/O of the PMIC or baseband, which has no power.

Per Table 2, the internal register of the OFF pin is set to HIGH after POR. Therefore, a HIGH-to-LOW transition (a falling edge) is triggered when FTL11639 completes POR. FTL11639 immediately starts the delay to turn off load switch ( $t_{SD}$ ). The VOUT pin changes from ON state to OFF state unless  $t_{SD}$  is interrupted (see Special Note on OFF Pin).

Similiarly, if the input to the OFF pin is logic HIGH when FTL11639 completes its POR, the VOUT pin remains ON.

Table 4. OFF Pin Behavior

| VOUT<br>(After POR) | Immedate<br>Input to OFF<br>after POR | Associated<br>Delay       | VOUT |

|---------------------|---------------------------------------|---------------------------|------|

| ON                  | HIGH                                  | N/A                       | ON   |

| ON                  | LOW                                   | $t_{SD} = 900 \text{ ms}$ | OFF  |

### Special Note on SYS\_WAKE Pin

The SYS\_WAKE pin is designed and characterized to handle high-voltage input for at least 20 V. Therefore, in application, a current-limiting resistor (i.e 100 k $\Omega$ ) is required between the SYS\_WAKE pin and the input signal regardless of input voltage.

## Adjustable Reset Delay with an External Resistor and DSR

The reset delay is adjustable by connecting a commonly available, low-power,  $\pm 5\%$ , RoHS-compliant resistor between the DELAY\_ADJ pin and the GND pin (see Table 5). To disable the adjustable delay feature, DELAY\_ADJ should be tied to  $V_{BAT}$  directly.

The reset delay is factory programmed at 7.5 s.

The additional power consumption caused by using an external resistor is negligible. The external resistor is normally disconnected and is enabled for milliseconds when /SR0 is pulled LOW.

This external adjustment provides an alternative for delay time for engineering and production at customer locations.

Fairchild can also factory program a wide range of turn-on times for  $V_{OUT}$  ( $t_{VON}$ ), timer delay before reset ( $t_{PHL1}$ ), reset timeout delay for  $V_{OUT}$  ( $t_{REC1}$ ), and load switch turn-off time ( $t_{OFF}$ ) to match customer applications. The external resistor ( $R_{ADJ}$ ) can be eliminated by factory programming, if desired.

For details, contact an authorized sales representative: <a href="http://www.fairchildsemi.com/cf/#Regional-Sales">http://www.fairchildsemi.com/cf/#Regional-Sales</a>.

Table 5. Delay Adjustment vs. External Resistor

| External Resistor R <sub>ADJ</sub> (kΩ) | Delay<br>Multiplier      | Adjusted Reset<br>Delay t <sub>PHL1</sub> _ADJ,<br>(Seconds) ±20% |

|-----------------------------------------|--------------------------|-------------------------------------------------------------------|

| Tie to GND<br>(No Resistor)             | 0.50 x t <sub>PHL1</sub> | 5.8                                                               |

| 3.9                                     | 0.75 x t <sub>PHL1</sub> | 8.6                                                               |

| 10                                      | 1.25 x t <sub>PHL1</sub> | 14.4                                                              |

| 22                                      | 1.50 x t <sub>PHL1</sub> | 17.3                                                              |

| 47                                      | 1.75 x t <sub>PHL1</sub> | 20.1                                                              |

| 120                                     | 2.00 x t <sub>PHL1</sub> | 23.0                                                              |

| Tie to V <sub>BAT</sub> (No Resistor)   | 1.00 x t <sub>PHL1</sub> | 11.5                                                              |

#### IntelliMAX™ Switch Inside the FTL11639

#### **Input Capacitor**

The IntelliMAX<sup>TM</sup> switch inside the reset timer doesn't require an input capacitor. To reduce device inrush current, a 0.1  $\mu$ F ceramic capacitor,  $C_{IN}$ , is recommended close to the  $V_{BAT}$  pin. A higher value of  $C_{IN}$  can be used to reduce the voltage drop experienced as the switch is turned on into a large capacitive load.

#### **Output Capacitor**

While the load switch works without an output capacitor; if parasitic board inductance forces  $V_{OUT}$  below GND when switching off, a 0.1  $\mu F$  capacitor,  $C_{OUT}$ , should be placed between  $V_{OUT}$  and GND.

#### **Fall Time**

Device output fall time can be calculated based on the RC constant of the external components, as follows:

$$t_F = R_L \times C_L \times 2.2 \tag{1}$$

where  $t_{\text{F}}$  is 90% to 10% fall time;  $R_{\text{L}}$  is output load; and  $C_{\text{L}}$  is output capacitor.

The same equation works for a device with a pull-down output resistor.  $R_L$  is replaced by a parallel connected pull-down and an external output resistor combination, calculated as:

$$t_F = \frac{R_L \times R_{PD}}{R_L + R_{PD}} \times C_L \times 2.2 \tag{2}$$

where  $t_F$  is 90% to 10% fall time;  $R_L$  is output load;  $R_{PD}{=}65\,\Omega$  is output pull-down resistor; and  $C_L$  is the output capacitor.

## **Resistive Output Load**

If resistive output load is missing, the IntelliMAX switch without a pull-down output resistor does not discharge the output voltage. Output voltage drop depends, in that case, mainly on external device leaks.

## **Application Specifics**

At maximum operational voltage ( $V_{BAT}$ =5.5 V), device inrush current might be higher than expected. Spike current should be taken into account if  $V_{BAT}$ >5 V and the output capacitor is much larger than the input capacitor. Input current  $I_{BAT}$  can be calculated as:

$$I_{BAT}(t) \approx \frac{V_{OUT}(t)}{R_{LOAD}} + (C_{LOAD} - C_{IN}) \frac{dV_{OUT}(t)}{dt}$$

(3)

where switch and wire resistances are neglected and capacitors are assumed ideal.

Estimating  $V_{OUT}(t)=V_{BAT}/10$  and using experimental formula for slew rate  $(dV_{OUT}(t)/dt)$ , spike current can be written as:

$$\max(I_{BAT}) = \frac{V_{BAT}}{10R_{LOAD}} + (C_{LOAD} - C_{IN})(0.05V_{BAT} - 0.255)$$

(4)

where supply voltage  $V_{\text{BAT}}$  is in volts; capacitances are in micro farads; and resistance is in ohms.

Example: If  $V_{BAT}$ =5.5 V,  $C_{LOAD}$ =100  $\mu$ F,  $C_{IN}$ =10  $\mu$ F, and  $R_{LOAD}$ =50  $\Omega$ ; calculate the spike current by:

$$\max(I_{BAT}) = \frac{5.5}{10 \times 50} + (100 - 10)(0.05 \times 5.5 - 0.255)A = 1.8A$$

Maximum spike current is 1.8 A, while average ramp-up current is:

$$I_{BAT}(t) \approx \frac{V_{OUT}(t)}{R_{LOAD}} + (C_{LOAD} - C_{IN}) \frac{dV_{BAT}(t)}{dt}$$

$\approx 2.75/50 + 100 \times 0.0022 = 0.275A$

#### **Output Discharge**

The device contains a R<sub>PD</sub>=65  $\Omega$  on-chip pull-down resistor for quick output discharge. The resistor is activated when the switch is turned off.

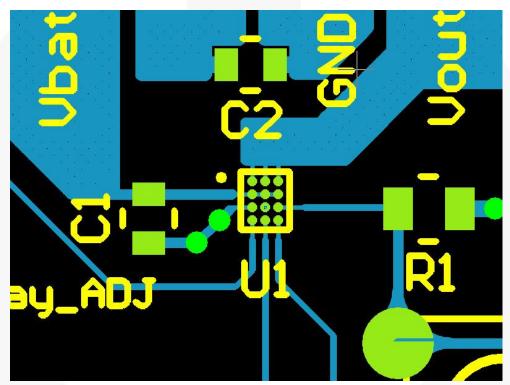

## **Recommended Layout**

For best thermal performance and minimal inductance and parasitic effects, keeping the input and output traces short and capacitors as close to the device as possible is recommended. Additional recommended layout considerations include:

- A1, A2, and A3 are interconnected at PCB, as close to the landing pad as possible.

- B1, B2, and B3 are interconnected at PCB, as close to the landing pad as possible.

- C1 (GND) is connected to GND plane of PCB.

- Reserve a pad for capacitor connection (C1) between VBAT and GND, if no input capacitor is planned.

- Reserve a pad for capacitor connection (C2) between V<sub>OUT</sub> and GND, if no output capacitor is planned.

- Use a dedicated V<sub>OUT</sub> or V<sub>BAT</sub> plane to improve thermal dissipation.

Figure 32. Sample Layout

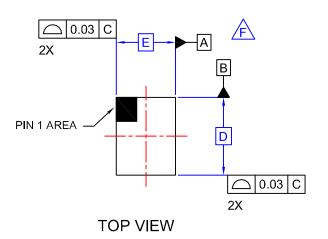

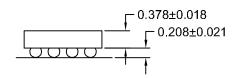

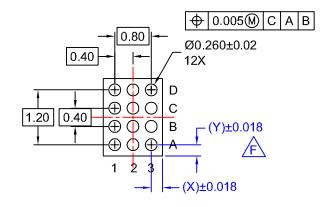

## **Product Specific Package Dimensions**

| D            | D E          |       | Υ     |

|--------------|--------------|-------|-------|

| 1.615 ±0.030 | 1.310 ±0.030 | 0.255 | 0.208 |

|   |     | REVISIONS                |         |                   |  |  |  |

|---|-----|--------------------------|---------|-------------------|--|--|--|

| F | REV | DESCRIPTION              | DATE    | APP'D / SITE      |  |  |  |

|   | 1   | Initial drawing release. | 8-19-09 | L. England / FSME |  |  |  |

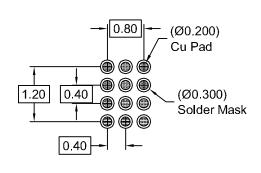

# RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

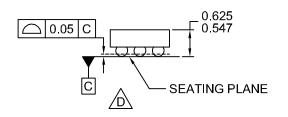

SIDE VIEWS

**BOTTOM VIEW**

## NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E. PACKAGE NOMINAL HEIGHT IS 586 MICRONS ±39 MICRONS (547-625 MICRONS).

F. FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

G. DRAWING FILENAME: MKT-UC012ACrev1.

| APPROVALS               | DATE    | FAIR                                               |      |                |         |     |

|-------------------------|---------|----------------------------------------------------|------|----------------|---------|-----|

| L. England              | 8-19-09 | SEMICO                                             |      |                |         |     |

| DFTG. CHK.<br>S. Martin | 8-19-09 | 400411 144 000 004 4004                            |      |                |         |     |

| ENGR. CHK.              |         | 12BALL WLCSP, 3X4 ARRAY<br>0.4MM PITCH, 250UM BALL |      |                |         |     |

|                         |         | U.4IVIIVI FITCH, 2500IVI BALI                      |      |                |         |     |

| PROJECTION INCH [MM]    |         | SCALE                                              | SIZE | DRAWING NUMBER |         | REV |

|                         |         | N/A                                                | N/A  | MKT-U          | JC012AC | 1   |

|                         |         | DO NOT SCALE DRAWING                               |      | SHEET 1 of 1   |         |     |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative